# **MIC5166**

# 3A High-Speed, Low-V<sub>IN</sub> DDR Terminator

#### **Features**

- · Operating Voltage Range:

- V<sub>DDQ</sub> Supply: 0.9V to 3.6V

- Bias Supply: 2.5V to 5.5V

- · High Bandwidth: Very Fast Transient Response

- Stable with Two 10 μF Ceramic Output Capacitors

- Two 10 μF Output Capacitors used in Most Applications

- · High Output Voltage Accuracy:

- 0.015% Line Regulation

- 1.5% Load Regulation

- · Logic Level Enable Input

- Power Good (PG)

- · Thermally Enhanced 3 mm x 3 mm DFN

- Junction Temperature Range –40°C to +125°C

- · This Device Meets DDR4 Requirements

#### **Applications**

- · Desktop Computers

- · Notebook Computers

- Datacom Systems

- · Servers

- · Video Cards

#### **General Description**

The MIC5166 is a 3A, high-speed, linear, low  $V_{\rm IN}$ , double data rate (DDR), memory terminator power supply. The part is small and requires small output capacitors, making it a tiny overall solution. This allows it to be conveniently placed close to the DDR memory, minimizing circuit board layout inductance that may cause excessive voltage ripple at the DDR memory.

The MIC5166 contains a precision voltage divider network in order to take in the  $V_{DDQ}$  voltage as a reference voltage and conveniently output the terminator voltage ( $V_{TT}$ ) at one half of the  $V_{DDQ}$  input voltage.

The MIC5166 is capable of sinking and sourcing up to 3A. It is stable with only two 10  $\mu$ F ceramic output capacitors. The part is available in a small 3 mm x 3 mm DFN thermally-enhanced package.

The MIC5166 has a high-side NMOS output stage offering very low output impedance, and very high bandwidth. The NMOS output stage offers a unique ability to respond very quickly to sudden load changes such as is required for DDR memory termination power supply applications.

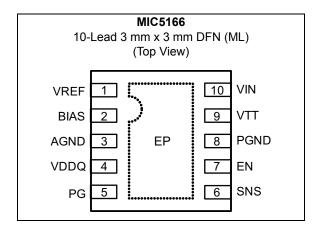

#### Package Type

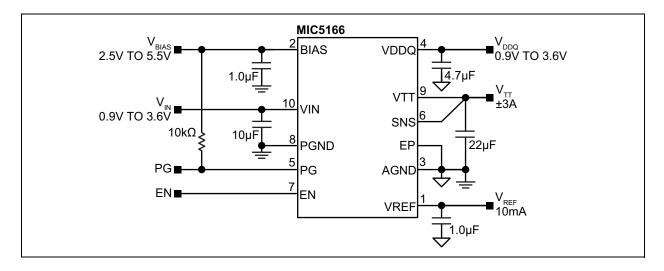

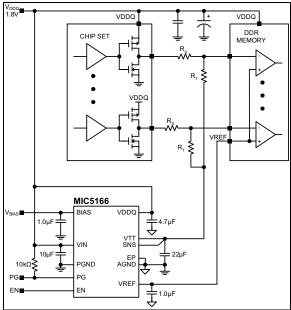

# **Typical Application Circuit**

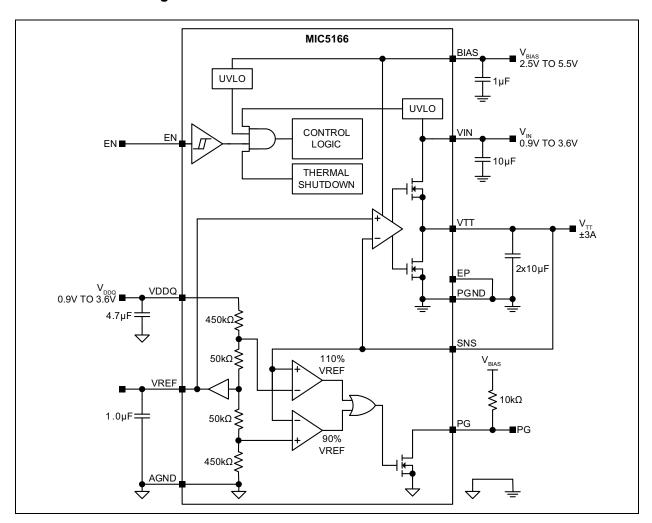

# **Functional Block Diagram**

#### 1.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| V <sub>BIAS</sub>                                                                     | 0.3V to +6V                |

|---------------------------------------------------------------------------------------|----------------------------|

| V <sub>BIAS</sub> V <sub>IN</sub>                                                     | –0.3V to V <sub>BIAS</sub> |

| V <sub>DDQ</sub>                                                                      | –0.3V to V <sub>IN</sub>   |

| V <sub>TT</sub>                                                                       | –0.3V to V <sub>IN</sub>   |

| V <sub>EN</sub>                                                                       | 0.3V to V <sub>BIAS</sub>  |

| V <sub>PG</sub>                                                                       | 0.3V to V <sub>BIAS</sub>  |

| PGND to AGND                                                                          | 0.3V to +0.3V              |

| Junction Temperature (T <sub>J</sub> )                                                | +150°C                     |

| Storage Temperature (T <sub>S</sub> )                                                 | –65°C to +150°C            |

| Lead Temperature (Soldering, 10 sec.)                                                 | +260°C                     |

| Continuous Power Dissipation (T <sub>A</sub> = +25°C; De-Rated 16.4 mW/°C above 25°C) |                            |

| Continuous Power Dissipation (T <sub>A</sub> = +85°C)                                 | 656 mW                     |

| ESD Rating (HBM, Note 1)                                                              |                            |

| Operating Ratings ††                                                                  |                            |

| Supply Voltage (V <sub>BIAS</sub> )                                                   | +2.5V to +5.5V             |

| Supply Voltage (V <sub>IN</sub> , Note 2)                                             |                            |

| Supply Voltage (V <sub>DDQ.</sub> Note 3)                                             |                            |

| Power Good Voltage (V <sub>PG</sub> )                                                 |                            |

| Enable Input Voltage (V <sub>EN</sub> )                                               |                            |

| Junction Temperature Range (T <sub>J</sub> )                                          |                            |

|                                                                                       | 40 6 10 + 125 6            |

| Package Thermal Resistance 3 mm x 3 mm DFN ( $\theta_{JC}$ )                          |                            |

**† Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

**†† Notice:** The device is not guaranteed to function outside its operating ratings.

- **Note 1:** Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5 k $\Omega$  in series with 100 pF.

- 2: If  $V_{BIAS} \le 3.6V$ , then  $V_{IN(MAX)} = V_{BIAS}$ .

- 3: If  $V_{BIAS} \le 4V$ , then  $V_{DDQ(MAX)} = 2 \times (V_{BIAS} 2.2V)$ . If  $V_{BIAS} > 4V$ , then  $V_{DDQ(MAX)} = 3.6V$ .

# **MIC5166**

# **ELECTRICAL CHARACTERISTICS**

**Electrical Characteristics:**  $V_{IN}$  = 1.5V,  $V_{BIAS}$  = 3.3V,  $V_{DDQ}$  = 1.5V,  $T_A$  = +25°C, unless noted. **Bold** values indicate  $-40^{\circ}C \le T_J \le +125^{\circ}C$ . Note 1

| Parameter                                                 | Sym.              | Min.  | Тур.  | Max. | Units | Conditions                                                                                                          |

|-----------------------------------------------------------|-------------------|-------|-------|------|-------|---------------------------------------------------------------------------------------------------------------------|

| Power Input Supply                                        |                   |       |       |      |       |                                                                                                                     |

| Input Voltage Range                                       | V <sub>IN</sub>   | 0.9   | _     | 3.6  | V     | _                                                                                                                   |

| Undervoltage Lockout Trip<br>Level                        | _                 | 0.625 | 0.8   | 0.9  | ٧     | V <sub>IN</sub> rising                                                                                              |

| UVLO Hysteresis                                           | _                 | _     | 150   | _    | mV    | _                                                                                                                   |

| Quiescent Supply Current                                  | I <sub>IN</sub>   | _     | 0.1   | 10   | μA    | I <sub>OUT</sub> = 0A                                                                                               |

| Shutdown Current                                          | I <sub>SHDN</sub> | _     | 0.1   | 5    | μA    | V <sub>EN</sub> = 0V                                                                                                |

| Bias Supply                                               |                   |       |       |      |       |                                                                                                                     |

| Bias Voltage Range                                        | V <sub>BIAS</sub> | 2.5   | _     | 5.5  | V     | _                                                                                                                   |

| Undervoltage Lockout Trip<br>Level                        | _                 | 1.9   | 2.23  | 2.33 | ٧     | V <sub>BIAS</sub> rising                                                                                            |

| UVLO Hysteresis                                           | _                 | _     | 70    | -    | mV    | _                                                                                                                   |

| Ovices and Committy Comment                               |                   | _     | 1.6   | 3    | ^     | I <sub>OUT</sub> = 1 mA                                                                                             |

| Quiescent Supply Current                                  | I <sub>BIAS</sub> | _     | 1.6   | 3    | mA    | I <sub>OUT</sub> = 1A                                                                                               |

| Shutdown Current                                          | I <sub>SHDN</sub> | _     | 0.1   | 5    | μA    | V <sub>EN</sub> = 0V                                                                                                |

| V <sub>TT</sub> Output                                    |                   |       |       |      |       |                                                                                                                     |

| V <sub>TT</sub> Accuracy                                  | _                 | -25   | _     | 25   | mV    | Variation from $V_{REF}$ , $I_{OUT} = -2A$ to $2A$                                                                  |

|                                                           | _                 | _     | 1.5   | 2.1  | %     | V <sub>SNS</sub> = 0.75V, I <sub>OUT</sub> = +10 mA to +3A                                                          |

| Load Regulation                                           |                   | -1.8  | -1.4  | _    |       | V <sub>SNS</sub> = 0.75V, I <sub>OUT</sub> = -10 mA to -3A                                                          |

| Live Box Inflor                                           | _                 | -0.05 | 0.005 | 0.05 | %/V   | $V_{IN}$ = 1.5V to 3.6V, $V_{BIAS}$ = 5.5V, $I_{OUT}$ = 100 mA                                                      |

| Line Regulation                                           |                   | -0.1  | 0.015 | 0.17 |       | $V_{IN}$ = 1.5V, $V_{BIAS}$ = 2.5V to 5.5V, $I_{OUT}$ = 100 mA                                                      |

| V <sub>REF</sub> Output                                   |                   |       |       |      |       |                                                                                                                     |

| V <sub>REF</sub> Voltage Accuracy                         | $V_{REF}$         | -1    | _     | 1    | %     | Variation from ( $V_{DDQ}/2$ ),<br>$I_{REF} = -10$ mA to 10 mA,<br>$V_{REF}$ Output = 0.6V (DDR4), $I_{OUT} = 0$ A. |

| <b>Bias Supply Dropout Volt</b>                           | age               |       |       |      |       |                                                                                                                     |

|                                                           |                   | _     | 1.15  | l    |       | I <sub>OUT</sub> = 100 mA                                                                                           |

| Dropout Voltage<br>(V <sub>BIAS</sub> – V <sub>TT</sub> ) | $V_{DO}$          | _     | 1.25  | 1    | V     | I <sub>OUT</sub> = 500 mA                                                                                           |

| (*BIA2 *11)                                               |                   |       | 1.65  | 2.2  |       | I <sub>OUT</sub> = 3A                                                                                               |

| Enable Control                                            |                   |       |       |      |       |                                                                                                                     |

| EN Logic High Level                                       | $V_{IH}$          | 1.2   | _     | _    | V     | Logic high                                                                                                          |

| EN Logic Low Level                                        | $V_{IL}$          | _     | _     | 0.2  | V     | Logic low                                                                                                           |

| EN Current                                                | I <sub>EN</sub>   | _     | 1.0   | _    | μA    | V <sub>EN</sub> = 0.2V                                                                                              |

| EN Current                                                |                   | _     | 6.0   |      |       | V <sub>EN</sub> = 1.2V                                                                                              |

| Start-Up Time                                             | t <sub>SU</sub>   | _     | 55    |      | μs    | From EN pin going high to $V_{TT}$ 90% of $V_{REF}$                                                                 |

Note 1: Specification for packaged product only.

# **ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Characteristics:**  $V_{IN}$  = 1.5V,  $V_{BIAS}$  = 3.3V,  $V_{DDQ}$  = 1.5V,  $T_A$  = +25°C, unless noted. **Bold** values indicate  $-40^{\circ}\text{C} \le T_J \le +125^{\circ}\text{C}$ . Note 1

| Parameter                              | Sym.                | Min.         | Тур. | Max. | Units | Conditions                                                 |  |

|----------------------------------------|---------------------|--------------|------|------|-------|------------------------------------------------------------|--|

| Short-Current Protection               |                     |              |      |      |       |                                                            |  |

| Sourcing Current Limit                 | I <sub>LIM</sub>    | 3.1          | 4.9  | 7.8  | Α     | V <sub>IN</sub> = 2.7V, V <sub>TT</sub> = 0V               |  |

| Sinking Current Limit                  | I <sub>LIM</sub>    | <b>-</b> 3.1 | -4.9 | -7.8 | Α     | $V_{IN}$ = 2.7V, $V_{TT}$ = $V_{IN}$                       |  |

| Internal FETs                          |                     |              |      |      |       |                                                            |  |

| Top MOSFET                             | R <sub>DS(ON)</sub> | _            | 130  | 190  | mΩ    | Source, I <sub>OUT</sub> = 3A (V <sub>TT</sub> to PGND)    |  |

| Bottom MOSFET                          | R <sub>DS(ON)</sub> | l            | 130  | 190  | mΩ    | Sink, $I_{OUT} = -3A (V_{IN} \text{ to } V_{TT})$          |  |

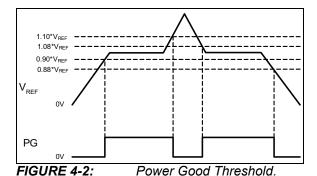

| Power Good (PG)                        |                     |              |      |      |       |                                                            |  |

| PG Window                              | _                   | ≥90          |      | ≤110 | %     | Threshold percent of V <sub>TT</sub> from V <sub>REF</sub> |  |

| Hysteresis                             | _                   | -            | 2    | _    | %     | _                                                          |  |

| PG Output Low Voltage                  | _                   | 1            | 430  | _    | mV    | I <sub>PG</sub> = 4 mA (sinking)                           |  |

| PG Leakage Current                     | _                   | -            | _    | 1.0  | μA    | $V_{PG}$ = 5.5V, $V_{SNS}$ = $V_{REF}$                     |  |

| Thermal Protection                     | Thermal Protection  |              |      |      |       |                                                            |  |

| Overtemperature<br>Shutdown            | _                   | _            | 150  | _    | °C    | T <sub>J</sub> rising                                      |  |

| Overtemperature<br>Shutdown Hysteresis | _                   | _            | 10   | _    | °C    | _                                                          |  |

Note 1: Specification for packaged product only.

# **MIC5166**

# **TEMPERATURE SPECIFICATIONS**

| Parameters                        | Sym.              | Min. | Тур. | Max. | Units | Conditions         |  |

|-----------------------------------|-------------------|------|------|------|-------|--------------------|--|

| Temperature Ranges                |                   |      |      |      |       |                    |  |

| Junction Temperature Range        | $T_J$             | -40  | _    | +125 | °C    | _                  |  |

| Maximum Junction Temperature      | $T_{J(MAX)}$      | _    | _    | +150 | °C    | _                  |  |

| Lead Temperature                  | _                 | _    | _    | +260 | °C    | Soldering, 10 sec. |  |

| Storage Temperature Range         | T <sub>S</sub>    | -65  | _    | +150 | °C    | _                  |  |

| Package Thermal Resistances       |                   |      |      |      |       |                    |  |

| Thermal Resistance, 3x3 DFN 10-Ld | $\theta_{\sf JC}$ |      | 28.7 | _    | °C/W  | _                  |  |

| Thermal Resistance, 3x3 DFN 10-Ld | $\theta_{JA}$     |      | 60.7 | _    | °C/W  | _                  |  |

Note 1: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation will cause the device operating junction temperature to exceed the maximum +125°C rating. Sustained junction temperatures above +125°C can impact the device reliability.

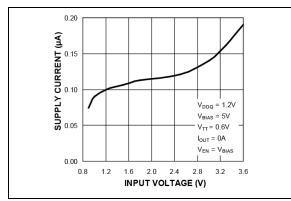

#### 2.0 TYPICAL PERFORMANCE CURVES

Note:

The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**FIGURE 2-1:**  $V_{IN}$  Operating Supply Current vs. Input Voltage.

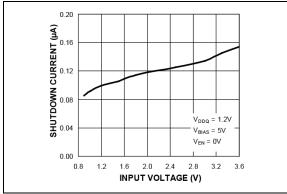

**FIGURE 2-2:** V<sub>IN</sub> Shutdown Current vs. Input Voltage.

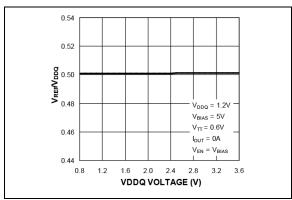

**FIGURE 2-3:**  $V_{REF}/V_{DDQ}$  Tracking Ratio vs.  $V_{DDQ}$  Voltage.

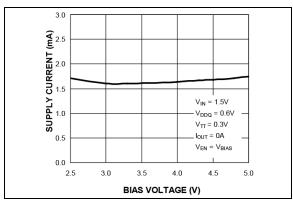

**FIGURE 2-4:** V<sub>BIAS</sub> Operating Supply Current vs. BIAS Voltage.

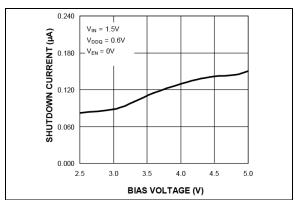

**FIGURE 2-5:** V<sub>BIAS</sub> Shutdown Current vs. BIAS Voltage.

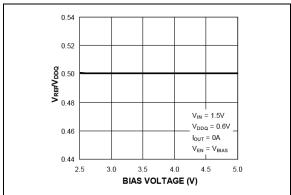

**FIGURE 2-6:**  $V_{REF}/V_{DDQ}$  Tracking Ratio vs. BIAS Voltage.

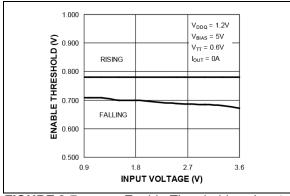

FIGURE 2-7: Enable Threshold vs. Input Voltage.

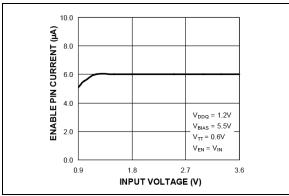

FIGURE 2-8: Enable Pin Current vs. Input Voltage.

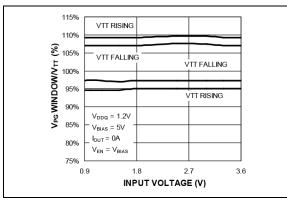

**FIGURE 2-9:** Power Good Window/V<sub>TT</sub> Ratio vs. Input Voltage.

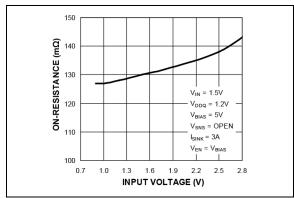

FIGURE 2-10: Top MOSFET On-Resistance vs. Input Voltage.

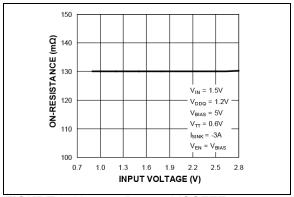

FIGURE 2-11: Bottom MOSFET On-Resistance vs. Input Voltage.

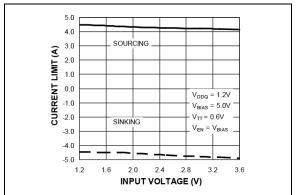

FIGURE 2-12: Current Limit vs. Input Voltage.

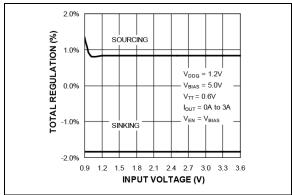

FIGURE 2-13: Load Regulation vs. Input Voltage.

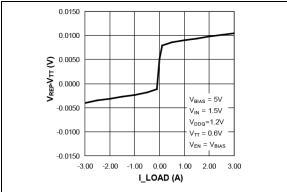

FIGURE 2-14:  $V_{REF} - V_{TT}$  vs. I\_Load.

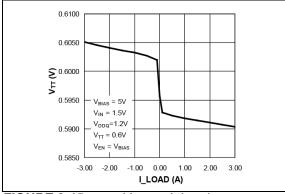

FIGURE 2-15: V<sub>TT</sub> vs. I\_Load.

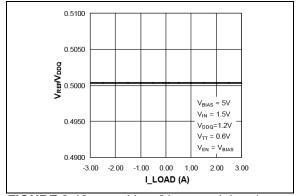

FIGURE 2-16: V<sub>REF</sub>/V<sub>DDQ</sub> vs. I\_Load.

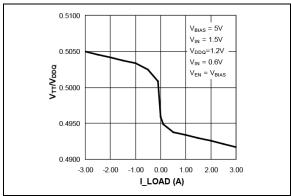

FIGURE 2-17: V<sub>TT</sub>/V<sub>DDQ</sub> vs. I\_Load.

**FIGURE 2-18:** V<sub>IN</sub> Operating Supply Current vs. Temperature.

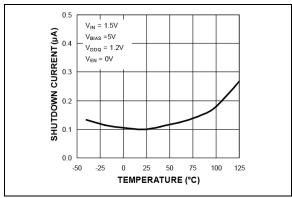

**FIGURE 2-19:** Temperature.

V<sub>IN</sub> Shutdown Current vs.

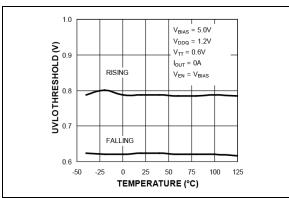

**FIGURE 2-20:** Temperature.

V<sub>IN</sub> UVLO Threshold vs.

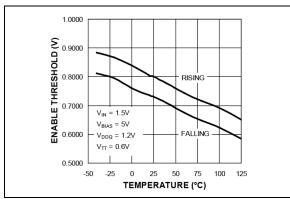

**FIGURE 2-21:** Temperature.

Enable Threshold vs.

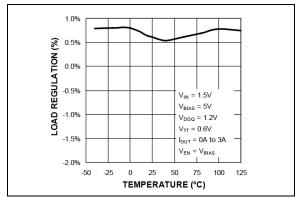

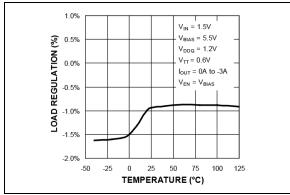

**FIGURE 2-22:**

Sourcing Load Regulation

vs. Temperature.

**FIGURE 2-23:** Temperature.

Sinking Load Regulation vs.

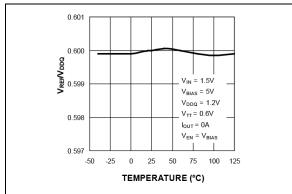

**FIGURE 2-24:**

V<sub>REF</sub>/V<sub>DDQ</sub> Tracking Ration

vs. Temperature.

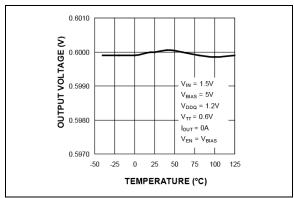

**FIGURE 2-25:**

Output Voltage vs.

Temperature.

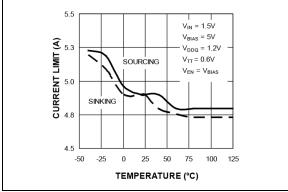

**FIGURE 2-26:**

Current Limit vs.

Temperature.

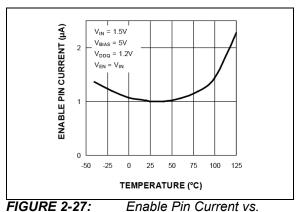

Temperature.

Enable Pin Current vs.

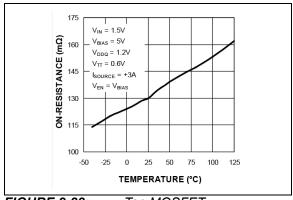

**FIGURE 2-28:** Top MOSFET On-Resistance vs. Temperature.

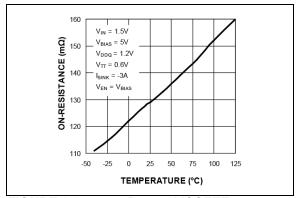

**FIGURE 2-29: Bottom MOSFET** On-Resistance vs. Temperature.

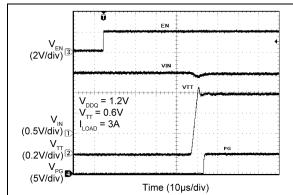

**FIGURE 2-30:**

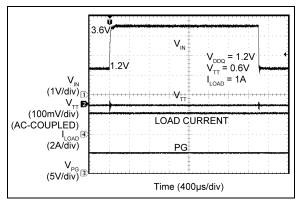

EN Turn-On.

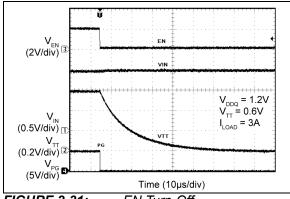

FIGURE 2-31: EN Turn-Off.

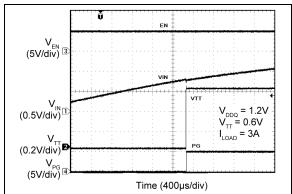

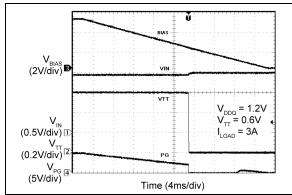

FIGURE 2-32: V<sub>IN</sub> Turn-On (UVLO).

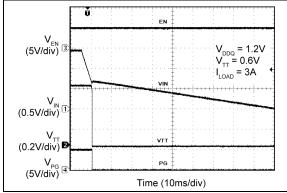

FIGURE 2-33: V<sub>IN</sub> Turn-Off UVLO.

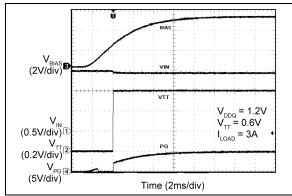

FIGURE 2-34: V<sub>BIAS</sub> Turn-On (UVLO).

FIGURE 2-35: V<sub>BIAS</sub> Turn-Off (UVLO).

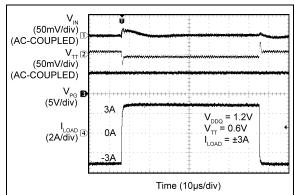

FIGURE 2-36: Load Transient (±3A).

FIGURE 2-37: Line Transient.

# 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| Pin Number | Pin Name | Description                                                                                                                                                                                                                                                                          |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VREF     | Reference Voltage. This output provides an output of the internal reference voltage $V_{DDQ}/2$ . The $V_{REF}$ output is used to provide the reference voltage for the memory chip. Connect a 1.0 $\mu$ F capacitor to ground at this pin. This pin can sink and source 10 mA.      |

| 2          | BIAS     | BIAS Supply Voltage. The BIAS supply is the power MOSFET gate drive supply voltage and the supply bus for the IC. The BIAS voltage must be greater than (V $_{TT}$ + 2.2V). A 1.0 $\mu$ F ceramic capacitor from the BIAS pin to PGND must be placed next to the IC.                 |

| 3          | AGND     | Analog Ground. Internal signal ground for all low-power circuits.                                                                                                                                                                                                                    |

| 4          | VDDQ     | Input Supply. VDDQ is connected to an internal precision divider that provides the $V_{REF}$ . Connect a 4.7 $\mu F$ capacitor to ground at this pin.                                                                                                                                |

| 5          | PG       | Power Good. This is an open-drain output that indicates when the output voltage is within $\pm 10\%$ of the reference voltage. The PG flag is asserted typically with 65 $\mu$ s delay when the enable is set low or when the output goes outside $\pm 10\%$ the window threshold.   |

| 6          | SNS      | Feedback. Input to the error amplifier.                                                                                                                                                                                                                                              |

| 7          | EN       | Enable. Logic level control of the output. Logic high enables the MIC5166 and a logic low shuts down the MIC5166. In the off state, supply current of the device is greatly reduced (typically 0.2 µA). The EN pin should not be left open.                                          |

| 8          | PGND     | Power Ground. Internal ground connection to the source of the internal, low-side drive, N-channel MOSFET.                                                                                                                                                                            |

| 9          | VTT      | Power Output. This is the connection to the source of the internal high-side N-channel MOSFET and drain of the low-side N-channel MOSFET. This is a high-frequency, high-power connection, therefore two 10 $\mu$ F output capacitors must be placed as close to the IC as possible. |

| 10         | VIN      | High-Side N-Channel MOSFET Drain Connection. The $V_{\text{IN}}$ operating voltage range is from 0.9V to 3.6V. An input capacitor between the VIN pin and the PGND is required as close to the chip as possible.                                                                     |

| EP         | ePAD     | Exposed Pad. Must be connected to a GND plane for best thermal performance.                                                                                                                                                                                                          |

#### 4.0 FUNCTIONAL DIAGRAM

DDR memory requires two power supplies: one for the memory chip, referred to as  $V_{DDQ}$ , and the other for a termination supply,  $V_{TT}$ , which is one-half  $V_{DDQ}$ . With memory speeds in excess of 300 MHz, the memory system bus must be treated as a transmission line. To maintain good signal integrity the memory bus must be terminated to minimize signal reflections. Figure 4-1 shows the simplified termination circuit. Each control, address and data lines have these termination resistors  $R_S$  and  $R_T$  connected to them.

FIGURE 4-1: DDR Memory Termination Circuit.

Bus termination provides a means to increase signaling speed while maintaining good signal integrity. The termination network consists of a series resistor ( $R_{\rm S}$ ) and a terminating resistor ( $R_{\rm T}$ ). Values of  $R_{\rm S}$  range between  $10\Omega$  to  $30\Omega$  with a typical of  $22\Omega$ , while  $R_{\rm T}$  ranges from  $22\Omega$  to  $28\Omega$  with a typical value of  $25\Omega$ .  $V_{REF}$  must maintain half  $V_{DDQ}$  with a ±1% tolerance, while  $V_{TT}$  will dynamically sink and source current to maintain a termination voltage of ±40 mV from the  $V_{REF}$  line under all conditions. This method of bus termination reduces common-mode noise, settling time, voltage swings, EMI/RFI, and improves slew rates.

$V_{DDQ}$  powers all the memory ICs, memory drivers and receivers for all the memory bits in the DDR memory system. The MIC5166 regulates  $V_{TT}$  to  $V_{DDQ}/2$  during sourcing or sinking current.

The memory bits are not usually all at a logic high or logic low at the same time, so the  $V_{TT}$  supply is usually not sinking or sourcing -3A or +3A current continuously.

#### 4.1 V<sub>TT</sub>

$V_{TT}$  is regulated to  $V_{REF}.$  Due to high-speed signaling, the load current seen by  $V_{TT}$  is constantly changing. To maintain adequate transient response, two 10  $\mu F$  ceramic capacitors are required. The proper placement of ceramic capacitors is important to reduce both ESR and ESL such that high-current and high-speed transients do not exceed the dynamic voltage tolerance requirement of  $V_{TT}.$  The ceramic capacitors provide current during the fast edges of the bus transition. Using several smaller ceramic capacitors distributed near the termination resistors is important to reduce the effects of PCB trace inductance.

# 4.2 V<sub>DDQ</sub>

The  $V_{DDQ}$  input on the MIC5166 is used to create the internal reference voltage for  $V_{TT}$ . The reference voltage is generated from an internal resistor divider network of two 500 k $\Omega$  resistors, generating a reference voltage  $V_{REF}$  that is  $V_{DDQ}/2$ . The  $V_{DDQ}$  input should be Kelvin connected as close as possible to the memory supply voltage.

Because the reference is simply  $V_{DDQ}/2$ , any perturbations on  $V_{DDQ}$  will also appear at half the amplitude on the reference. For this reason, a 4.7  $\mu$ F ceramic capacitor is required on the  $V_{DDQ}$  supply. This will aid performance by improving the source impedance over a wide frequency range.

#### 4.3 Sense

The sense (SNS) pin provides the path for the error amplifier to regulate  $V_{TT}$ . The SNS input must also be Kelvin connected to the  $V_{TT}$  bypass capacitors. If the SNS input is connected too close to the MIC5166, the IR drop of the PCB trace can cause the  $V_{TT}$  voltage at the memory chip to be too low. Placing the MIC5166 as close as possible to the DDR memory will improve the load regulation performance.

#### 4.4 Enable

The MIC5166 features an active-high enable input (EN) that allows on-off control of the regulator. The current through the device reduces to near "zero" when the device is shutdown, with only <0.2  $\mu A$  of leakage current. The EN input may be directly tied to  $V_{BIAS}.$  The active-high enable pin uses CMOS technology and the enable pin cannot be left floating. A floating enable pin may cause an indeterminate state on the output.

#### 4.5 Power Good (PG)

The power good (PG) output provides an undervoltage and overvoltage fault flag for the  $V_{TT}$  output. The PG output remains high as long as  $V_{TT}$  is within  $\pm 10\%$  range of  $V_{REF}$  and goes low if the output moves beyond this range.

The PG has an open-drain output. A pull-up resistor must be connected to  $V_{BIAS}$ ,  $V_{IN}$ , or an external source. The external source voltage must not exceed the maximum rating of the pin. The PG pin can be connected to another regulator's enable pin for sequencing of the outputs.

# 4.6 V<sub>BIAS</sub> Requirement

A 1  $\mu$ F ceramic input capacitor is required on the V<sub>BIAS</sub> pin. To achieve the ultra-fast transient response, the MIC5166 uses an all N-channel power output stage as shown in the Functional Block Diagram. The high-side N-channel MOSFET requires the V<sub>BIAS</sub> voltage to be 2.2V higher than the V<sub>TT</sub> to be able to fully enhance the high-side MOSFET.

# 4.7 V<sub>IN</sub> Requirement

$V_{IN}$  is used to supply the rail voltage for the high-side N-channel power output stage. It is normally connected to  $V_{DDQ},$  but it can be connected to a lower voltage to reduce power dissipation. In this case, the input voltage must be higher than the  $V_{TT}$  voltage to ensure that the output stage is not operating in dropout.

#### 5.0 COMPONENT SELECTION

# 5.1 Input Capacitor

A 10  $\mu F$  ceramic input capacitor is all that is required for most applications if it is close to a bulk capacitance.

The input capacitor must be placed on the same side of the board and next to the MIC5166 to minimize the dropout voltage and voltage ringing during transient and short-circuit conditions. It is also recommended that each capacitor to be connected to the PGND directly, not through vias. X7R or X5R dielectric ceramic capacitors are recommended because of their temperature performance. X7R-type capacitors change capacitance by 15% over their operating temperature range and are the most stable type of ceramic capacitors. Z5U and Y5V dielectric capacitors change value by as much as 50% and 60% respectively over their operating temperature ranges. To use a ceramic chip capacitor with Y5V dielectric, the value must be much higher than an X7R ceramic.

#### 5.2 Output Capacitor

As part of the frequency compensation, the MIC5166 requires two 10  $\mu$ F ceramic output capacitors for best transient performance. To improve transient response, any other type of capacitor can be placed in parallel as long as the two 10  $\mu$ F ceramic output capacitors are placed next to the MIC5166.

The output capacitor type and placement criteria are the same as the input capacitor. See the Input Capacitor section for a detailed description.

#### 5.3 Thermal Considerations

The MIC5166 is packaged in the 3 mm x 3 mm DFN, a package that has excellent thermal performance. This maximizes heat transfer from the junction to the exposed pad (ePAD) that connects to the ground plane. The size of the ground plane attached to the exposed pad determines the overall thermal resistance from the junction to the ambient air surrounding the printed circuit board.

#### 5.4 Thermal Design

The most complicated design parameters to consider are thermal characteristics. Thermal design requires the following application-specific parameters:

- Maximum ambient temperature (T<sub>A</sub>)

- Output current (I<sub>OUT</sub>)

- Output voltage (V<sub>OUT</sub>)

- Input voltage (V<sub>IN</sub>)

- Ground current (I<sub>GND</sub>)

First, calculate the power dissipation of the regulator from these numbers and the device parameters from this data sheet.

#### **EQUATION 5-1:**

$$P_D = (V_{IN} - V_{TT}) \times I_{OUT} + (V_{BIAS} \times I_{GND})$$

Where:

$I_{OUT}$  = Approximated by using numbers from the Electrical Characteristics or Typical Performance Curves.

For example, given an expected maximum ambient temperature ( $T_A$ ) of 70°C with  $V_{IN}$  = 1.2V,  $V_{BIAS}$  = 3.3V,  $V_{TT}$  = 0.9V, and  $I_{OUT}$  = 3A, first calculate the expected  $P_D$  using Equation 5-1:

#### **EQUATION 5-2:**

$$P_D = (1.2V - 0.9V) \times 3A + 3.3V \times 0.0016A = 0.90528W$$

Next, determine the junction temperature for the expected power dissipation above using the thermal resistance ( $\theta_{JA}$ ) of the 10-pin 3 mm x 3 mm DFN (YML) adhering to the following criteria for the PCB design (1oz. copper and 100 mm<sup>2</sup> copper area for the MIC5166):

#### **EQUATION 5-3:**

$$T_J = (\theta_{JA} \times P_D) + T_A$$

$$T_J = (60.7^{\circ}C/W \times 0.90528W) + 70^{\circ}C$$

$$T_J = 124.95^{\circ}C$$

To determine the maximum power dissipation allowed that would not exceed the IC's maximum junction temperature (125°C) when operating at a maximum ambient temperature of 70°C:

#### **EQUATION 5-4:**

$$P_{D(MAX)} = (T_{J(MAX)} - T_A)/\theta_{JA}$$

$$P_{D(MAX)} = (125^{\circ}C - 70^{\circ}C)/(60.7^{\circ}C/W) = 0.9061W$$

#### 5.5 Thermal Measurements

It is always wise to measure the IC's case temperature to make sure that it is within its operating limits. Although this might seem like a very elementary task, it is very easy to get erroneous results. The most common mistake is to use the standard thermocouple that comes with the thermal voltage meter. This thermocouple wire gauge is large, typically 22 gauge, and behaves like a heat sink, resulting in a lower case measurement.

There are two suggested methods for measuring the IC case temperature: a thermocouple or an infrared thermometer. If a thermocouple is used, it must be constructed of 36 gauge wire or higher to minimize the wire heat sinking effect. In addition, the thermocouple tip must be covered in either thermal grease or thermal glue to make sure that the thermocouple junction makes good contact to the case of the IC. This thermocouple from Omega (5SC-TT-K-36-36) is adequate for most applications.

To avoid this messy thermocouple grease or glue, an infrared thermometer is recommended. Most infrared thermometers' spot size is too large for an accurate reading on small form factor ICs. However, an IR thermometer from Optris has a 1 mm spot size, which makes it ideal for the 3 mm x 3 mm DFN package.

#### 5.6 Sequencing

The following diagrams illustrate methods for connecting MIC5166s to achieve sequencing requirements:

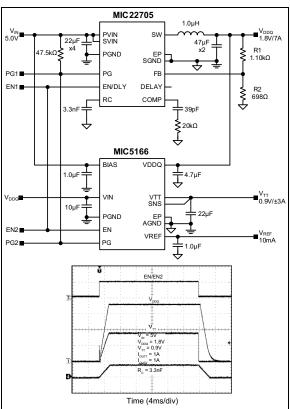

FIGURE 5-1: Turn-On Sequence with Soft-Start ( $R_C = 3.3 \text{ nF}$ ).

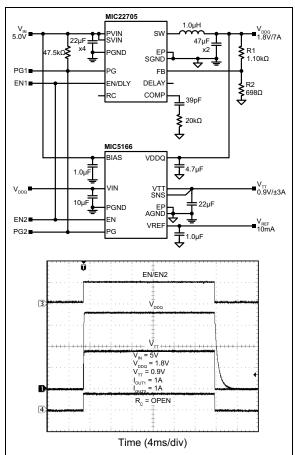

**FIGURE 5-2:** Turn-On Sequence without Soft-Start ( $R_C$  = Open).

#### 6.0 PCB LAYOUT GUIDELINES

To minimize EMI and output noise, follow these layout recommendations.

PCB layout is critical to achieve reliable, stable, and efficient performance. A ground plane is required to control EMI and minimize the inductance in power, signal, and return paths.

The following guidelines should be followed to ensure proper operation of the MIC5166 converter.

#### 6.1 IC

- The 10 µF ceramic capacitor, which is connected to the VIN pin, must be located right at the IC. The VDDQ pin is very noise sensitive and placement of the capacitor is very critical. Use wide traces to connect to the VDDQ and AGND pins.

- The signal ground pin (AGND) must be connected directly to the ground planes. Do not route the AGND pin to the PGND Pad on the top layer.

- Place the IC close to the point-of-load (POL).

- Use wide traces to route the input and output power lines.

- Signal and power grounds should be kept separate and connected at only one location.

#### 6.2 Input Capacitor

- A 10 µF X5R or X7R dielectric ceramic capacitor is recommended on each of the VIN pins for bypassing.

- Place the input capacitors on the same side of the board and as close to the IC as possible.

- Keep both the VIN pin and PGND connections short.

- Place several vias to the ground plane close to the input capacitor ground terminal.

- Use either X7R or X5R dielectric input capacitors.

Do not use Y5V or Z5U type capacitors.

- Do not replace the ceramic input capacitor with any other type of capacitor. Any type of capacitor can be placed in parallel with the input capacitor.

- If a Tantalum input capacitor is placed in parallel with the input capacitor, it must be recommended for switching regulator applications and the operating voltage must be derated by 50%.

- In hot-plug applications, a Tantalum or Electrolytic bypass capacitor must be used to limit the overvoltage spike seen on the input supply with power is suddenly applied.

#### 6.3 Output Capacitor

- Use a wide trace to connect the output capacitor ground terminal to the input capacitor ground terminal.

- Phase margin will change as the output capacitor value and ESR changes. Contact the factory if the output capacitor is different from what is shown in the BOM.

- The feedback divider network must be place close to the IC with the bottom of R2 connected to AGND.

- The feedback trace should be separate from the power trace and connected as close as possible to the output capacitor. Sensing a long high current load trace can degrade the DC load regulation.

# 7.0 EVALUATION BOARD SCHEMATICS

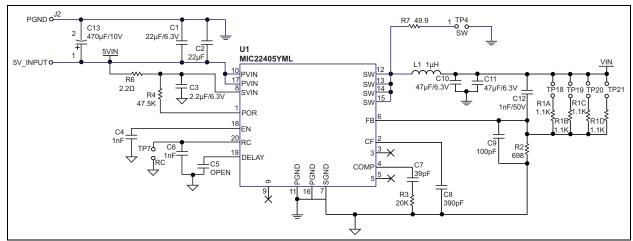

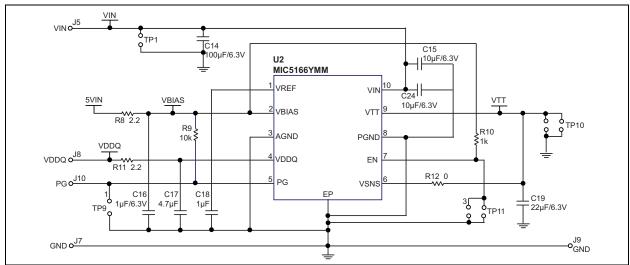

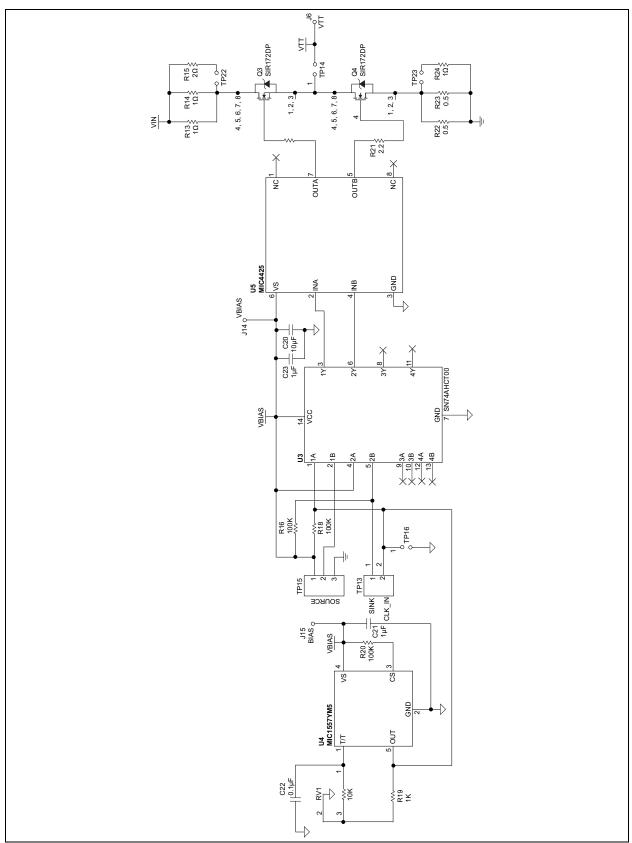

FIGURE 7-1: U1 Schematic.

FIGURE 7-2: U2 Schematic.

FIGURE 7-3: Evaluation Board Schematic.

TABLE 7-1: BILL OF MATERIALS

| Item                  | Part Number        | Manufacturer | Description                                | Qty. |  |

|-----------------------|--------------------|--------------|--------------------------------------------|------|--|

| 04.00                 | 08056D226MAT       | AVX          |                                            |      |  |

| C1, C2,<br>C19        | C2012X5R0J226K     | TDK          | 22 μF, 6.3V, ceramic capacitor, X5R, 0805  | 3    |  |

| 010                   | GRM21BR60J226ME39L | Murata       |                                            |      |  |

|                       | 08056D225KAT2A     | AVX          |                                            |      |  |

| C3                    | C2012X5R0J225K     | TDK          | 2.2µF, 6.3V, ceramic capacitor, X5R, 0805  | 1    |  |

|                       | GRM21BR60J225KA01L | Murata       |                                            |      |  |

| 04.00                 | 06035C102KAT       | AVX          |                                            |      |  |

| C4, C6,<br>C12        | C1608X7R1H102K     | TDK          | 1 nF, 50V, ceramic capacitor, X7R, 0603    | 3    |  |

| 012                   | GRM188R71H102KA01D | Murata       |                                            |      |  |

|                       | 06035A390JAT2A     | AVX          |                                            |      |  |

| C7                    | C1608C0G1H390J     | TDK          | 39 pF, 50V, ceramic capacitor, NPO, 0603   | 1    |  |

|                       | GRM1885C1H390JA01D | Murata       |                                            |      |  |

|                       | 06035A391JAT2A     | AVX          |                                            |      |  |

| C8                    | C1608C0G1H391J     | TDK          | 390 pF, 50V, ceramic capacitor, NPO, 0603  |      |  |

|                       | GRM188R71H391KA01D | Murata       |                                            |      |  |

|                       | 06035A101JAT2A     | AVX          |                                            |      |  |

| C9                    | C1608C0G1H101J     | TDK          | 100 pF, 50V, ceramic capacitor, NPO, 0603  | 1    |  |

|                       | GRM1885C1H101JA01D | Murata       |                                            |      |  |

|                       | 12066D476MAT2A     | AVX          |                                            | 2    |  |

| C10, C11              | C3216X5R0J476M     | TDK          | 47μF, 6.3V, ceramic capacitor, X5R,1206    |      |  |

|                       | GRM31CR60J476ME19L | Murata       |                                            |      |  |

|                       | 12106D107MAT2A     | AVX          |                                            |      |  |

| C14                   | C3225X5R0J107M     | TDK          | 100 μF, 6.3V, ceramic capacitor, X5R, 1210 | 1    |  |

|                       | GRM32ER60J107ME20L | Murata       |                                            |      |  |

|                       | 06036D106MAT       | AVX          |                                            |      |  |

| C15, C20,<br>C24      | FP3-1R0-R          | TDK          | 10 μF, 6.3V, ceramic capacitor, X5R, 0603  | 3    |  |

| C24                   | GRM188R60J106ME47D | Murata       | _                                          |      |  |

|                       | 06036D105KAT2A     | AVX          |                                            |      |  |

| C16, C18,<br>C21, C23 | C1608X5R0J105K     | TDK          | 1 μF, 6.3V, ceramic capacitor, X5R, 0603   | 4    |  |

| C21, C23              | GRM188R60J105KA01D | Murata       | _                                          |      |  |

|                       | 06036D475KAT2A     | AVX          |                                            |      |  |

| C17                   | C1608X5R0J475M     | TDK          | 4.7 μF, 6.3V, ceramic capacitor, X5R, 0603 | 1    |  |

|                       | C1608X5R0J475M     | Murata       | _                                          |      |  |

| C5                    | _                  | _            | N.U. 0603 ceramic capacitor                | 1    |  |

|                       | 06035C104KAT2A     | AVX          |                                            |      |  |

| C22                   | C1608X7R1H104K     | TDK          | 0.1 μF, 50V, ceramic capacitor, X7R, 0603  | 1    |  |

|                       | GRM188R71H104KA93D | Murata       | _                                          |      |  |

| C13                   | EEU-FC1A471        | Panasonic    | 470 μF/10V, Elect., 20%, 8x11.5, Radial    | 1    |  |

| L1                    | FP3-1R0-R          | Cooper       | 1 μH,6.26A Inductor                        | 1    |  |

| Q3, Q4                | NDS8425            | Fairchild    | MOSFET, N-CH 20V 7.4A 8-SOIC               | 2    |  |

| R1A                   | CRCW0603300RFKEA   | Vishay Dale  | 300Ω, resistor, 1%, 0603                   | 1    |  |

| R1B                   | CRCW06031101FKEA   | Vishay Dale  | 510Ω, resistor, 1%, 0603                   | 1    |  |

| R1C                   | CRCW0603806RFKEA   | Vishay Dale  | 806Ω, resistor, 1%, 0603                   | 1    |  |

| R1D                   | CRCW06031K10FKEA   | Vishay Dale  | 1.1 kΩ, resistor, 1%, 0603                 | 1    |  |

# **MIC5166**

# TABLE 7-1: BILL OF MATERIALS (CONTINUED)

| Item                        | Part Number        | Manufacturer | Description                                       | Qty. |

|-----------------------------|--------------------|--------------|---------------------------------------------------|------|

| R2                          | CRCW0603698RFKEA   | Vishay Dale  | 698Ω, resistor, 1%, 0603                          | 1    |

| R3                          | CRCW06032002FKEA   | Vishay Dale  | 20 kΩ, resistor, 1%, 0603                         | 1    |

| R4                          | CRCW06034752FKEA   | Vishay Dale  | 47.5 kΩ, resistor, 1%, 0603                       | 1    |

| R6, R8,<br>R11, R17,<br>R21 | CRCW06032R20RFKEA  | Vishay Dale  | 2.2Ω, resistor, 1%, 0603                          | 5    |

| R7                          | CRCW060349R9RFKEA  | Vishay Dale  | 49.9Ω, resistor, 1%, 0603                         | 1    |

| R9                          | CRCW06031002FKEA   | Vishay Dale  | 10 kΩ, resistor, 1%, 0603                         | 1    |

| R10, R19                    | CRCW06031K00FKEA   | Vishay Dale  | 1 kΩ, resistor, 1%, 0603                          | 2    |

| R12                         | CRCW0603000RFKEA   | Vishay Dale  | 0Ω, resistor, 1%, 0603                            | 1    |

| R13, R14,<br>R24            | CRCW25121R00FKEGHP | Vishay Dale  | 1Ω, resistor, 1.5W, 1%, 2512                      | 3    |

| R15                         | CRCW25122R00JNEG   | Vishay Dale  | 2Ω, resistor, 1.5W, 1%, 2512                      | 1    |

| R16, R18,<br>R20            | CRCW06031003FKEA   | Vishay Dale  | 100 kΩ, resistor, 1%, 0603                        | 3    |

| R22, R23                    | LR2512-R50FW       | Vishay Dale  | 0.5Ω, resistor, 1.5W, 1%, 2512                    | 2    |

| RV1                         | PV36W103C01B00     | Murata       | Pot, 10 kΩ, 0.5W, 9.6x5x10                        | 1    |

| U1                          | MIC22405YML        | Microchip    | 4A, Synchronous Buck Regulator                    | 1    |

| U2                          | MIC5166YMM         | Microchip    | 3A High-Speed Low V <sub>IN</sub> DDR Terminator  | 1    |

| U3                          | SN74AHCT00RGYR     | TI           | Quad, 2IN Pos-NAND Gate, 14-pin, QFN              | 1    |

| U4                          | MIC1557YM5         | Microchip    | 5 MHz RC Timer Oscillator                         | 1    |

| U5                          | MIC4425            | Microchip    | 3A Dual Inverting and Non-Inverting MOSFET Driver | 1    |

# 7.1 PCB Layout Recommendations

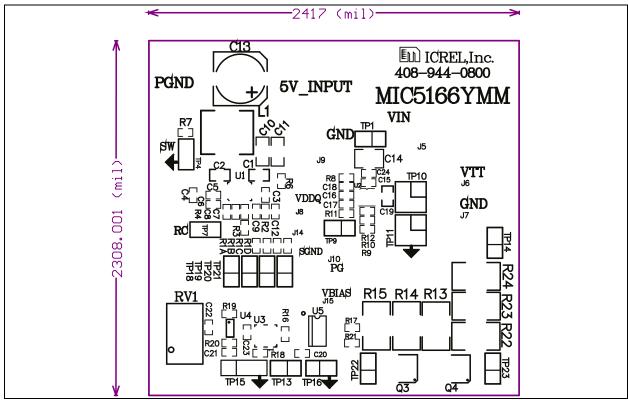

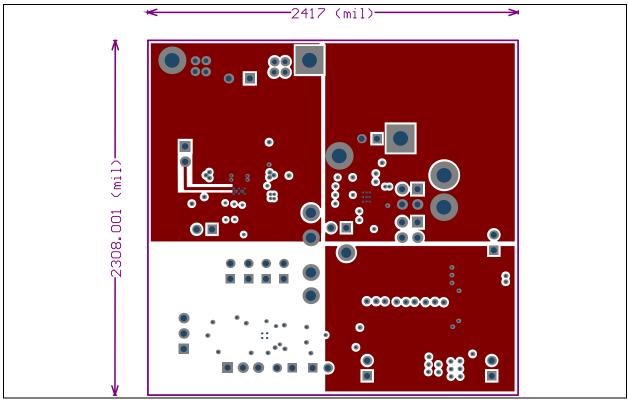

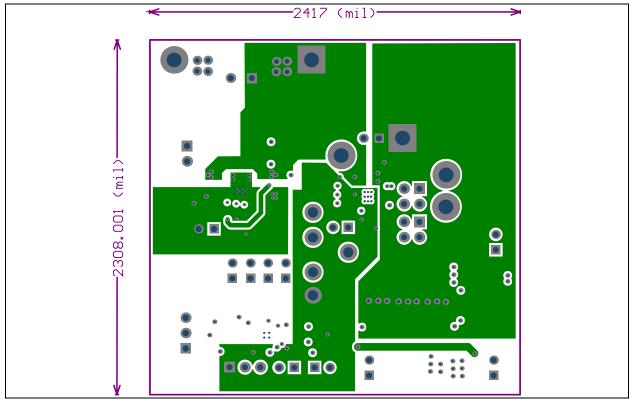

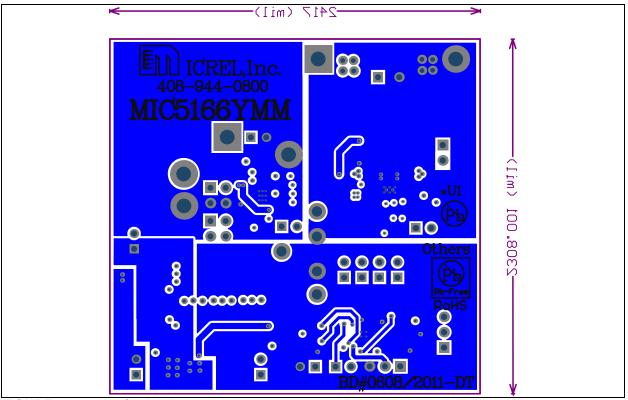

FIGURE 7-4: Top Silk.

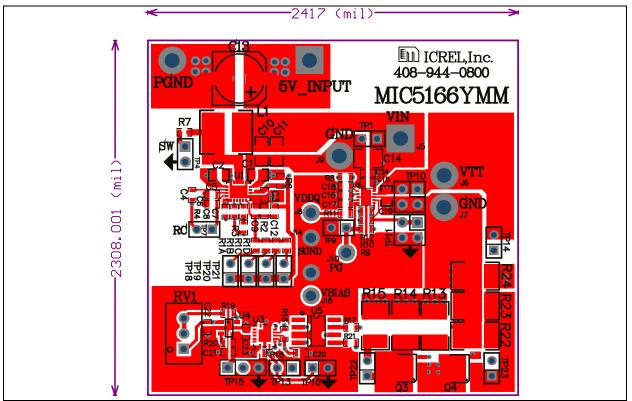

FIGURE 7-5: Copper Layer 1.

FIGURE 7-6: Copper Layer 2.

FIGURE 7-7: Copper Layer 3.

FIGURE 7-8: Copper Layer 4.

FIGURE 7-9: Bottom Silk.

#### 8.0 PACKAGING INFORMATION

# 8.1 Package Marking Information

10-Lead DFN\*

Example

**Legend:** XX...X Product code or customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

e3 Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator ((e3)) can be found on the outer packaging for this package.

•, ▲, ▼ Pin one index is identified by a dot, delta up, or delta down (triangle mark).

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. Package may or may not include the corporate logo.

Underbar (\_) and/or Overbar (¯) symbol may not be to scale.

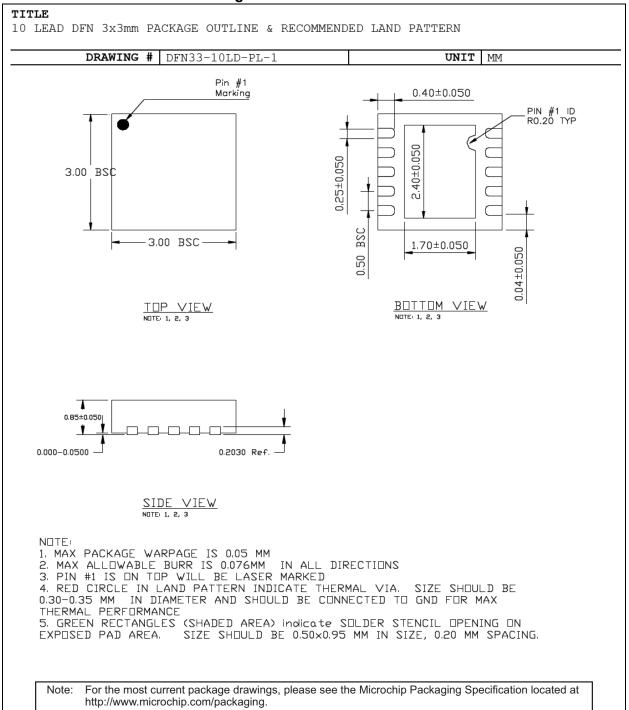

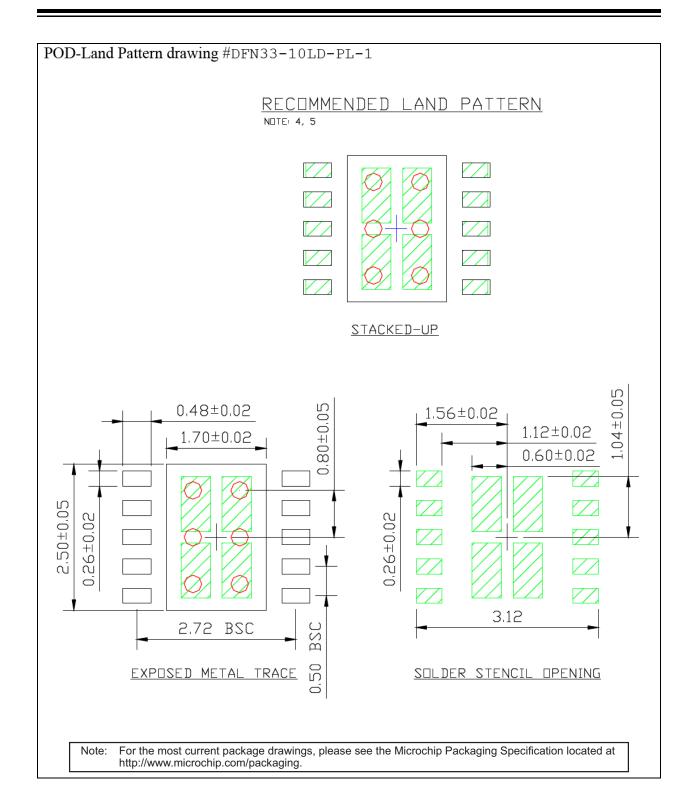

### 10-Lead 3 mm x 3 mm DFN Package Outline & Recommended Land Pattern

# APPENDIX A: REVISION HISTORY

# **Revision A (October 2018)**

- Converted Micrel document MIC5166 to Microchip data sheet template DS20006085A.

- Minor grammatical text changes throughout.

# Revision B (March 2019)

- EN and PG pin names/numbers corrected in Typical Application Circuit and Figure 7-2.

- Updated V<sub>TT</sub> Accuracy values in the Electrical Characteristics table.

NOTES:

## PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

Device XX-<u>XX</u> <u>X</u> Part No. Junction Package Media Type Temp. Range Device: MIC5166: 3A High-Speed, Low  $V_{\text{IN}}$  DDR Terminator Junction -40°C to +125°C, RoHS-Compliant Temperature Range: Package: 10-Lead 3 mm x 3 mm x 0.9 mm DFN ML = 5,000/Reel Media Type: TR = Note: DFN is a green, RoHS-compliant package. Lead finish is NiPdAu. Mold compound is Halogen free.

Examples:

a) MIC5166YML-TR: MIC5166, -40°C to +125°C

Temperature Range, 10-Lead 3 mm x 3 mm DFN,

5,000/Reel

Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the

Tape and Reel option.

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A. Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM, net. PICkit, PICtail, PowerSmart, PureSilicon. QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

$\ @$  2018 - 2019, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-4306-3

# **Worldwide Sales and Service**

#### **AMERICAS**

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support: http://www.microchip.com/ support

Web Address:

www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614

Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas Addison, TX

Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523

Fax: 949-462-9608 Tel: 951-273-7800

**Raleigh, NC** Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

China - Chongqing Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

**China - Nanjing** Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen

Tel: 86-755-8864-2200 China - Suzhou

Tel: 86-186-6233-1526 China - Wuhan

Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

**China - Xiamen** Tel: 86-592-2388138

China - Zhuhai Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

Korea - Daegu

Tel: 82-53-744-4301 **Korea - Seoul** Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

**Austria - Wels** Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820