**SE050**

Plug & Trust Secure Element Rev. 3.1 — 15 December 2020

Product data sheet

# 504931

# 1 Introduction

The SE050 is a ready-to-use IoT secure element solution. It provides a root of trust at the IC level and it gives an IoT system state-of-the-art, edge-to-cloud security capability right out of the box.

SE050 allows for securely storing and provisioning credentials and performing cryptographic operations for security critical communication and control functions. SE050 is versatile in IoT security use cases such as secure connection to public/private clouds, device-to-device authentication or protection of sensor data.

SE050 has an independent Common Criteria EAL 6+ security certification up to OS level and supports both RSA & ECC asymmetric cryptographic algorithms with high key length and future proof ECC curves. The latest security measures protect the IC even against sophisticated non-invasive and invasive attack scenarios.

The SE050 is a turnkey solution that comes with Java Card operating system and an applet optimized for IoT security use cases pre-installed. This is complemented by a comprehensive product support package, enabling fast time to market & easy design-in with Plug & Trust middleware for host applications, easy to use development kits, reference designs, and extensive documentation for product evaluation.

The SE050 is a product platform that comes in several pin-to-pin compatible product variants, see [4].

Additional information on the integration can be found in several application notes on www.nxp.com. Also see [3].

#### 1.1 SE050 use cases

- · Secure connection to public/private clouds, edge computing platforms, infrastructure

- Device-to-device authentication

- · Secure data protection

- Secure commissioning support

- Secure CL/MIFARE/Wi-Fi interactions

- Device ID for blockchain

- Secure key storage

- · Secure provisioning of credentials

- · Ecosystem protection

#### 1.2 SE050 target applications

- Smart Industry

- Smart Home

- Smart Cities

- Smart Supply Chains

SE050

**Plug & Trust Secure Element**

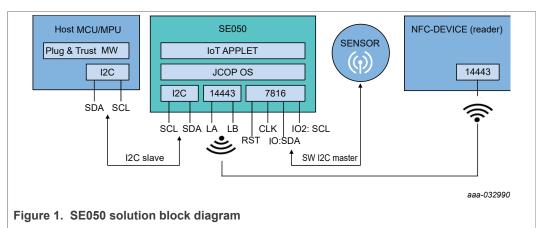

**Note:** SE050 is designed to be used as a part of an IoT system. It works as an auxiliary security device attached to a host controller. The host controller communicates with SE050 through an I<sup>2</sup>C interface (with the host controller being the master and the SE050 being the slave). Besides the mandatory connection to the host controller, the SE050 device can optionally be connected to a sensor node or similar element through a separate I<sup>2</sup>C interface. In this case, the SE050 device is the master and the sensor node the slave. Lastly, SE050 has a connection for a native contactless antenna, providing a wireless interface to an external device like a smartphone.

### 1.3 SE050 naming convention

The following table explains the naming conventions of the commercial product name of the SE050 platform. Every SE050 product gets assigned a commercial name, which includes application specific data.

The SE050 commercial names have the following format.

#### SE05yagddd/Zrrff

All letters are explained in Table 1 .

| Table 1. | SE050 | commercial | name | format |

|----------|-------|------------|------|--------|

|----------|-------|------------|------|--------|

| Variable | Meaning           | Values              | Description                                                                             |

|----------|-------------------|---------------------|-----------------------------------------------------------------------------------------|

| У        | JCOP version      | 0                   |                                                                                         |

| а        | Applet Config     | A<br>B<br>C<br>D    | Configuration options with different key provisioning options, see [4]                  |

| g        | Temperature range | 1<br>2              | standard operational ambient temperature<br>1 = -25 °C - 85 °C ,<br>2 = -40 °C - 105 °C |

| ddd      | Delivery Type     | HQ1                 | HX2QFN20                                                                                |

| Zrrff    |                   | Letters and numbers | NXP internal code to identify individual configurations                                 |

# 2 Features and benefits

### 2.1 Key benefits

- Plug & Trust for fast and easy design with complete product support package

- Easy integration with different MCU & MPU platforms and OS´ (Linux, RTOS, Windows, Android, etc.)

- Turnkey solution ideal for system-level security without the need to write security code

- · Secure credential injection for root of trust at IC level

- Secure, zero-touch connectivity to public & private clouds

- Real end-to-end security, from sensor to cloud

- Ready-to-use example code for each of the key use cases

#### 2.2 Key features

The SE050 is based on NXP's Integral Security Architecture 3.0<sup>™</sup> providing a secure and efficient protection against various security threats. The efficiency of the security measures is proven by a Common Criteria EAL6+ certification.

The SE050 operates fully autonomously based on an integrated Javacard operating system and applet. Direct memory access is possible by the fixed functionalities of the applet only. With that, the content from the memory is fully isolated from the host system.

- Built on NXP Integral Security Architecture 3.0<sup>™</sup>

- Uses advanced 40 nm silicon foundry technology

- CC EAL 6+ certified HW and OS as environment to run NXP IoT applications, supporting fully encrypted communications and secured lifecycle management

- Effective protection against advanced attacks, including Power Analysis and Fault Attacks of various kinds

- Multiple logical and physical protection layers, including metal shielding, end-to-end encryption, memory encryption, tamper detection

- Support for RSA and ECC asymmetric cryptography algorithms, future proof curves and high key length, e.g. Brainpool, Edwards and Montgomery curves

- Support for AES and DES symmetric cryptographic algorithms for encryption and decryption

- HMAC, CMAC, SHA-1, SHA-224/256/384/512 operations

- Various options for key derivation functions, including HKDF, MIFARE KDF, PRF (TLS-PSK)

- Optional extended temperature range for industrial applications (-40 °C to +105 °C)

- Small footprint HX2QFN20 package (3x3 mm)

- Standard physical interface I<sup>2</sup>C slave (High-speed mode, 3.4 Mbps), I<sup>2</sup>C master (Fast mode, 400 kbps). Both can be active at the same time

- Dedicated CL wireless interface for IoT use cases simplifying configuration set-up, maintenance in the field and late stage configuration

- Secured user flash memory up to 50 kB for secure data or key storage

- Support for SCP03 protocol (bus encryption and encrypted credential injection) to securely bind the host with the secure element

- Support for applet level secure messaging channels to allow end-to-end encrypted communication in multi-tenant ecosystems

| Product | data | sheet |

|---------|------|-------|

|         |      |       |

# 2.3 Features in detail

| Categories         | Subcategory                          | Value                                                 |

|--------------------|--------------------------------------|-------------------------------------------------------|

| Standards          | Security certification               | CC EAL6+ (HW+JCOP)                                    |

|                    | JavaCard version                     | 3.0.5                                                 |

|                    | GlobalPlatform specification version | GP 2.3.1                                              |

| Cryptography       | ECC                                  | ECDSA, ECDH, ECDHE, ECDAA,<br>EdDSA                   |

|                    | MAC                                  | HMAC, secure HMAC, CMAC                               |

|                    | Hash                                 | SHA-1, SHA-224, SHA-256, SHA-384,<br>SHA-512          |

|                    | Key derivation                       | HKDF, PBKDF2, PRF (TLS-PSK),<br>CMAC (MIFARE-AES-KDF) |

|                    | AES                                  | AES (128, 192, 256)                                   |

|                    | 3DES                                 | 2К, 3К                                                |

|                    | RSA                                  | RSA cipher for de-/encryption (up to 4096 bit)        |

| Crypto curves      | ECC                                  | ECC NIST (192 to 521 bit)                             |

|                    |                                      | Brainpool (160 to 512 bit)                            |

|                    |                                      | Twisted Edwards Ed25519 /<br>Montgomery Curve25519    |

|                    |                                      | Koblitz (192 to 256 bit)                              |

|                    |                                      | Barreto-Naehrig Curve 256 bit                         |

| User memory        | I                                    | 50 kB                                                 |

| Memory reliability |                                      | up to 100 Mio write cycles / 25 years                 |

| Interfaces         | I <sup>2</sup> C Slave               | High-speed mode (3.4 Mbps)                            |

|                    | I <sup>2</sup> C Master              | Fast Mode (400 kbit/s)                                |

|                    | Contactless                          | ISO14443-A PICC                                       |

| Power saving modes | Power-Down (with state retention)    | < 500µA                                               |

|                    | Deep Power-Down (no state retention) | <5 µA                                                 |

| Temperature        | Standard                             | -25 - 85 °C, see Naming Conventions                   |

|                    | Extended                             | -40 - +105 °C, see Naming Convention                  |

| Packaging          | Plastic QFN                          | 3x3 mm (HX2QFN20)                                     |

# 3 Functional description

#### EdgeLock<sup>™</sup> SE050 ENABLEMENT PLUG AND TRUST MIDDLEWARE Android™. Linux<sup>®</sup>. FreeRTOS Linux, Windows<sup>®</sup>, macOS<sup>®</sup> PRE INTEGRATION TO MAIN USE CASE BASED EXAMPLE CODES, pyCLI TOOL EDGELOCK OS AND 2GO AGENT ANDROID T-FM PKCS1 OPC-UA MOTT TPM-TSS MCU, MPU KEYMASTER SEMSLite Arm<sup>®</sup> mbed™ TLS OpenSSL API EDGELOCK SE050 IoT APPLET JAVA CARD OPERATING SYSTEM HARDWARE aaa-034211

# 3.1 Functional diagram

Figure 2. SE050 functional diagram - example Open SSL

The SE050 uses  $I^2C$  as communication interface. <u>Section 4</u> gives more details. The SE050 commands are wrapped using the Smartcard T=1 over  $I^2C$  (T=10  $I^2C$ ) protocol. The detailed documentation of the SE050 commands (see [3]) and T=1 over  $I^2C$  protocol encapsulation is available on [1].

In order to simplify the product usage a host library which abstracts for SE050 commands and T=1 over  $I^2C$  protocol encapsulation is provided. The host library supporting various platforms is available for download including complete source code on the SE050 website.

SE050 IoT applet features a generic file system capable of securely storing secure objects and associated privilege management. All objects can either be stored in persistent memory or in RAM with the capability to securely export and import them to be stored in an externally provided storage. All secure objects feature basic file operations such as write, read, delete and update.

### 3.1.1 Random number generator

The SE050 IoT Applet provides random numbers using an AIS20 compliant pseudo random number generator (PRNG) with class DRG.3 generator initialized by a TRNG compliant to AIS31 class PTG.2. The PRNG is implemented according to NIST SP800-90A.

### 3.1.2 Supported secure object types

A secure object is an entry in the file system of SE050. Each secure object has certain features and capabilities. The following secure object types are available:

• Symmetric Key (AES, 3DES)

- ECC Key

- RSA Key

- HMAC Key

- Binary File

- User ID

- Counter

- Hash-Extend register

#### 3.1.2.1 Symmetric Key

The Symmetric Key object can securely store symmetric keys of AES 128, 192 and 256 bit, 2K3DES and 3K3DES. The following specific operations are available on symmetric key objects:

- Encrypt

- Decrypt

- Derive

- CMAC

- Secure Import

#### 3.1.2.2 ECC Key

The ECC Key object has the ability to securely store ECC keys of the following curves and key sizes:

- ECC NIST curve: NIST P-192, NIST P-224, NIST P-256, NIST P-384, NIST P-521

- ECC Brainpool curve: 160 bit, 192 bit, 224 bit, 256 bit, 320 bit, 384 bit, 512 bit

- Curve25519 (Montgomery) and Bi-rationally Equivalent Twisted Edwards Curve

- ECC Koblitz curves: secp160k1, secp192k1, secp224k1, secp256k1

- ECC Barreto-Naehrig 256 bit curve

The following operations are available on ECC key objects (not all operations are applicable to all curves):

- ECDSA/EdDSA Sign

- ECDSA/EdDSA Verify

- ECDH Generate Shared Secret/ECDHE

- ECDAA Sign

- ECDAA Verify

- Generate Key

- Secure Import

#### 3.1.2.3 RSA Key

The RSA Key object has the ability to securely store RSA Keys up to 4096 bit. The following specific operations are available on RSA key objects:

- RSA Sign

- RSA Verify

- RSA Encrypt

- RSA Decrypt

- RSA Generate Key

- Secure Import

#### 3.1.2.4 HMAC Key object

An HMAC key object allows to securely store an HMAC key. The following operations are supported on HMAC Key objects to compute an HMAC:

- Init

- Update

- Finalize

#### 3.1.2.5 Binary file objects

Binary file objects are byte arrays of a generic type. As in a standard file system, the values can be accessed using read/write operations.

#### 3.1.2.6 Counter Objects

Counter objects are special kinds of binary file objects with specific functionality interpreting the content of the file.

The supported operations for counters are:

- Set

- Get

- Increment

#### 3.1.2.7 Hash-Extend register

A hash-extend register secure object stores a hash over all data provided to that secure object. It therefore contains the complete history of values provided to that register since last reboot or since creation and can be used for attestation purposes.

#### 3.1.2.8 User ID secure object

User ID secure objects can be used to create sessions based on the User ID in cases where multi-tenant support without cryptographic credential usage is required.

#### 3.1.3 Access control

Each secure object can be linked to object specific access control policies. An access control policy associates a user identified by an authentication with a set of privileges such as read, write, ...

To scale the functionality into a broad range of ecosystems, a set of different authentication options is provided:

- User-ID based authentication

- · Symmetric key based authentication with secure messaging

- Asymmetric key based authentication with secure messaging At creation of a secure object, an optional set of policies is associated with that secure object. Each policy assigns a set of allowed operations on that object to an authentication object.

#### 3.1.4 Sessions and multi-threading

The SE050 IoT applet is prepared for ecosystems where multi-threading and multi-tenant use cases are needed on APDU level. To enable that, the applet supports 2 simultaneous sessions that can span full secure messaging sessions, self-authenticated APDUs for

tenants not requiring long-lasting sessions and on top one default session for single tenant use cases .

#### 3.1.5 Attestation and trust provisioning

SE050 applet comes with a set of trust provisioned root credentials allowing the owner of the device to securely attest all generated secure keys. Next to that, a customer has the possibility to define own attestation keys.

Attestation certificates signed by an attestation CA are included in certain SE050 configurations as documented in [4].

#### **3.1.6** Application support

For specific ecosystems, SE050 IoT applet has built-in crypto features to simplify the deployment of specific use cases such as

- MIFARE SAM functionality

- Wifi password protection

- ECC-Key and RSA-Key based cloud connectivity

- Secure Sensor readout using I<sup>2</sup>C master

- Remote attestation and trust provisioning

- Platform Configuration Registers

### 3.2 Credential Storage & Memory

Within SE050, all credentials and secure objects are stored inside a dynamic file structure. At creation, a user has to associate a file identifier with the object created. This identifier is then used in subsequent operations to access the object. The number of objects that can be allocated is only limited by the available memory in the system. After usage, objects can be deleted and the associated memory is freed up again.

There is also the possibility to create transient objects. Transient objects have an object descriptor stored in non-volatile memory, but the object content is stored in RAM. Together with the import/export functionality of SE050, transient objects can be used securely store secret keys in a remote memory system.

### 3.3 Ease of use configuration

Some generic SE050 variants are offered pre-configured for ease of use and can be used during development phase and in the field. With this customers have all keys pre-injected in SE050 that are required for the main use cases as e.g. cloud onboarding. For more information, see: [4]

### 3.4 Startup behaviour

If a supply voltage is applied to pins  $V_{in}$ ,  $V_{cc}$  within the specified supply voltage operating range or a RF field according to ISO/IEC 14443 is applied to antenna pins LA, LB the IC boots up.

During boot the IC checks for active interface according list below (in the order of the list):

ISO7816: If interface available for this product type, check CLK to be toggling, then wait for RST to be high

**SE050**

#### Plug & Trust Secure Element

- ISO14443: If interface available for this product type, check of RF field on LA, LB antenna pins

- I<sup>2</sup>C: If interface available for this product type, check if both I<sup>2</sup>C\_SDA, I<sup>2</sup>C\_SCL pins are at high level (internal weak pull-up active)

- The chosen interface is the only interface the SE050 will receive commands for processing. To select a different interface the IC needs to be reset.

# 4 Communication interfaces

# 4.1 I<sup>2</sup>C Interfaces

The SE050 has one  $I^2C$  interface supporting slave and one  $I^2C$  interface supporting master mode.

The I<sup>2</sup>C slave interface is the main communication interface of the device and is used by the host controller to send arbitrary APDUs to the device. It supports clock frequencies up to 3.4 MHz when operated in High-Speed Mode (HS). The I<sup>2</sup>C interface is using the Smartcard T=1 over I<sup>2</sup>C protocol.

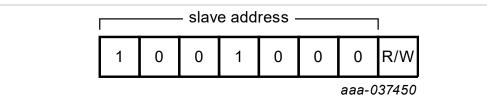

The default slave address of the SE050 is configured to 0x48.

Figure 3. Slave address

The I<sup>2</sup>C master interface is supposed to be used with slave devices that need to be securely written and read. This interface features a maximum SCL clock rate of 400 kHz.

# 4.1.1 Supported I<sup>2</sup>C frequencies

The SE050  $I^2C$  slave interface supports the  $I^2C$  high-speed mode with a maximum SCL clock of up to 3.4 MHz when clock stretching is enabled.

In case clock stretching is disabled the maximum supported SCL clock frequency is 1.7 MHz.

Clock stretching is enabled by default. Clock stretching will occur for frequencies higher than 600 kHz. In case clock stretching is not supported by the I<sup>2</sup>C master a dedicated configuration with disabled clock stretching has to be used to ensure the above mentioned maximum clock frequency.

The SE050 I<sup>2</sup>C master interface supports maximum 400 kHz SCL clock frequency.

### 4.2 ISO7816 and ISO14443 Interface

The SE050 supports in addition to the  $I^2C$  interface ISO7816<sup>1</sup> and ISO14443-A Smartcard interfaces. For the ISO7816 interface SmartCard protocols T=0 and T=1 are

© NXP B.V. 2020. All rights reserved.

<sup>1</sup> ISO7816 is not enabled in generic SE050 configurations (see [4], AN12436) but available on customer request.

supported. For the ISO14443 interface protocol T=CL is used. The supported resonance input capacitance is 56 pF. In addition one additional GPIO pad IO2 is supported.

The RST\_N pin can only be used as external reset source if the ISO7816 interface is enabled. If only the  $I^2C$  interface is enabled the RST\_N pad has no effect. If the SE050 is kept in reset state the current consumption is as defined for idle, see <u>Table 12</u>.

#### 5 Power-saving modes

The device provides two power-saving operation modes. The Power-down mode (with state retention) and the Deep Power-down mode (no state retention). These modes are activated via pad ENA (Deep Power-down mode) or by the SW (Power-down mode).

#### 5.1 Power-down mode

The Power-down mode has the following properties:

- All internal clocks are frozen

- CPU enters power-saving mode with program execution being stopped

- · CPU registers keep their contents

- RAM keeps its contents

The SE050 enters into Power-down mode by receiving "End of APDU session request" via the T=1 over  $I^2C$  protocol. In Power-down mode, all internal clocks are frozen. The IOs hold the logical states they had at the time Power-down mode was activated.

To exit from the Power-down mode an external interrupt edge must be triggered by a falling edge on  $I^2C\_SDA^2$ .

#### 5.2 Deep Power-down mode

The SE050 provides a special power-saving mode offering maximum power saving. This mode is activated by pulling enable PIN (ENA) to a logic zero level.

While in Deep Power-down mode the internal power and  $V_{OUT}$  is switched off completely and only the I<sup>2</sup>C pads stay supplied.

To leave the Deep Power-down mode pad ENA has to be pulled up to to a logic "1" level.

For usage of Deep Power-down mode the SE050 must be supplied via pin  $V_{\rm IN}$  and pin  $V_{\rm CC}$  needs to be supplied by pin  $V_{\rm OUT}.$

# 6 Ordering information

### 6.1 Ordering options

Table 3. SE050 Ordering information

| 12NC           | Type number      | SE050 Variant | Orderable part number |

|----------------|------------------|---------------|-----------------------|

| 9353 867 22472 | SE050A1HQ1/Z01SG | SE050A1       | SE050A1HQ1/Z01SGZ     |

| 9353 869 84472 | SE050A2HQ1/Z01SH | SE050A2       | SE050A2HQ1/Z01SHZ     |

2 In case ISO7816 is enabled a reset signal on RST\_N exits the Power-down mode. After wake-up from Power-down mode via RST\_N the device is in idle mode (see <u>Table 12</u>)

| Table 5. Sebse Ordering informationcommuted |                  |               |                       |  |

|---------------------------------------------|------------------|---------------|-----------------------|--|

| 12NC                                        | Type number      | SE050 Variant | Orderable part number |  |

| 935401587472                                | SE050D2HQ1/Z01PA | SE050D2       | SE050D2HQ1/Z01PAZ     |  |

| 9353 869 85472                              | SE050B1HQ1/Z01SE | SE050B1       | SE050B1HQ1/Z01SEZ     |  |

| 9353 869 86472                              | SE050B2HQ1/Z01SF | SE050B2       | SE050B2HQ1/Z01SFZ     |  |

| 9353 869 87472                              | SE050C1HQ1/Z01SC | SE050C1       | SE050C1HQ1/Z01SCZ     |  |

| 9353 869 88472                              | SE050C2HQ1/Z01SD | SE050C2       | SE050C2HQ1/Z01SDZ     |  |

#### Table 3. SE050 Ordering information...continued

#### Table 4. SE050 Ordering information for development kit

| 12NC           | Type number | Description                                                        |

|----------------|-------------|--------------------------------------------------------------------|

| 9353 832 82598 | OM-SE050ARD | SE050 Arduino-compatible development kit ,<br>SE050C configuration |

#### 6.2 Ordering SE050 samples

Samples can be ordered from NXP Semiconductors via nxp.com using the "Buy Direct" button on the product information page for SE050. Note that NXP Semiconductors can provide up to five pieces free of charge. Larger quantities have to be ordered commercially.

#### 6.3 Configuration

Detailed information about the configuration and available variants of the SE050 are available in a separate NXP Application Note, see [4]

# 7 Pinning information

# 7.1 Pinning

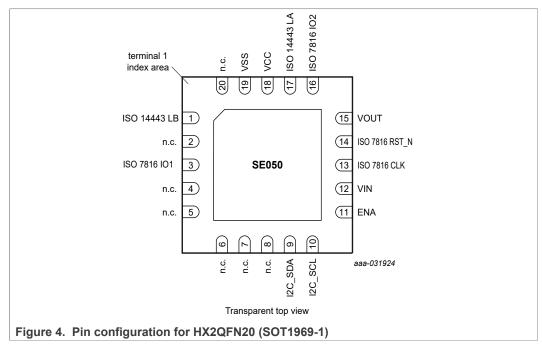

# 7.1.1 Pinning HX2QFN20

| Note: Terminal 1 index area is marked on the bottom with a notch on the center pad and |

|----------------------------------------------------------------------------------------|

| on the top with a printed dot.                                                         |

| Symbol               | Pin | Description                                                                                                                             |  |

|----------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| ISO 14443 LB         | 1   | ISO14443 Antenna Connection, if not used connect to $V_{SS}$                                                                            |  |

| n.c.                 | 2   | not connected                                                                                                                           |  |

| ISO 7816 IO1         | 3   | ISO 7816 IO or $I^2C$ master SDA, if not used n.c (recommended) or connect to $V_{CC}$                                                  |  |

| n.c.                 | 4   | not connected                                                                                                                           |  |

| n.c.                 | 5   | not connected                                                                                                                           |  |

| n.c.                 | 6   | not connected                                                                                                                           |  |

| n.c.                 | 7   | not connected                                                                                                                           |  |

| n.c.                 | 8   | not connected                                                                                                                           |  |

| I <sup>2</sup> C_SDA | 9   | I <sup>2</sup> C slave data, if not used n.c.                                                                                           |  |

| I <sup>2</sup> C_SCL | 10  | I <sup>2</sup> C slave clock, if not used n.c.                                                                                          |  |

| ENA                  | 11  | Deep Power-down mode enable, if not used then connect to $V_{CC}$                                                                       |  |

| V <sub>IN</sub>      | 12  | power supply voltage input for I <sup>2</sup> C pads and ISO 7816/14443 interface and logic supply in case Deep Power-down mode is used |  |

Product data sheet

| Symbol           | Pin | Description                                                                                                                                                 |

|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISO 7816 CLK     | 13  | ISO 7816 clock input, if not used then n.c (recommended) or connect to $V_{\text{CC}}$                                                                      |

| ISO 7816 RST_N   | 14  | ISO 7816 reset input low active, if not used then connect to Vcc or Vss                                                                                     |

| V <sub>OUT</sub> | 15  | supply voltage output to be connected with pad $V_{CC}$ on PCB level, if Deep Power-down mode is used. N. c. if not used.                                   |

| ISO 7816 IO2     | 16  | ISO7816 IO2 pad or I <sup>2</sup> C master SCL. I if not used n.c (recommended) or connect to $V_{OUT}$ .                                                   |

| ISO 14443 LA     | 17  | ISO14443 antenna connection, if not used then connect to $V_{SS}$                                                                                           |

| V <sub>cc</sub>  | 18  | logic and ISO7816/ISO14443 interface power supply voltage input, to be connected with pad $V_{\text{OUT}}$ on PCB level, if Deep Power-down mode to be used |

| V <sub>SS</sub>  | 19  | ground                                                                                                                                                      |

| n.c.             | 20  | not connected                                                                                                                                               |

#### Table 5. Pin description HX2QFN20...continued

The center pad of the IC is not connected, although it is recommended to connect it to ground for thermal reasons.

Reference voltage for ISO 1816 IO1, CLK, RST is  $V_{CC}$ ; for I<sup>2</sup>C SDL and SCL reference voltage is  $V_{IN}$  and for IO2 it is  $V_{OUT}$ .

### 8 Package

SE050 is offered in HX2QFN20 package. The dimensions are 3 mm x 3 mm x 0,32 mm with a 0,4 mm pitch.

Please refer to the package data sheet [2], SOT1969-1.

# 9 Marking

| Table 6. Marking codes |                                          |  |  |

|------------------------|------------------------------------------|--|--|

| Type number            | Marking code                             |  |  |

| Sx050                  | Line A: S50                              |  |  |

|                        | Line B: **** (**** = 4-digit Batch code) |  |  |

|                        | Line C: nDyww                            |  |  |

|                        | D: RHF-2006 indicator                    |  |  |

|                        | n: Assembly Center                       |  |  |

|                        | Y: Year                                  |  |  |

|                        | WW: Week                                 |  |  |

# **10 Packing information**

#### 10.1 Reel packing

The SE050 product is available in tape on reel.

#### Table 7. Reel packing options

| Symbol   | Parameter       | Numbers of units per reel |

|----------|-----------------|---------------------------|

| HX2QFN20 | 7" tape on reel | 3000                      |

# **11** Electrical and timing characteristics

The electrical interface characteristics of static (DC) and dynamic (AC) parameters for pads and functions used for  $I^2C$  are in accordance with the NXP  $I^2C$  specification (see [1]).

# 12 Limiting values

#### Table 8. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). Voltages are referenced to V<sub>SS</sub> (ground = 0 V).

| Symbol                            | Parameter                                                | Conditions                                                                                                      |     | Min  | Max       | Unit |

|-----------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|------|-----------|------|

| V <sub>IN</sub> , V <sub>cc</sub> | supply voltage                                           |                                                                                                                 |     | -0.3 | +6<br>[1] | V    |

| VI                                | input voltage                                            | any signal pad                                                                                                  |     | -0.3 | +6        | V    |

| lı –                              | input current                                            | pad I <sup>2</sup> C_SDA, I <sup>2</sup> C_SCL                                                                  |     | -    | 10        | mA   |

| lo                                | output current                                           | pad I <sup>2</sup> C_SDA, I <sup>2</sup> C_SCL                                                                  |     | -    | 10        | mA   |

| l <sub>lu</sub>                   | latch-up current                                         | $V_{I} < 0 V \text{ or } V_{I} > V_{IN}, V_{cc}$                                                                |     | -    | 100       | mA   |

| $V_{esd\_hbm}$                    | electrostatic discharge voltage<br>(Human Body Model)    | pads V <sub>CC</sub> , V <sub>SS</sub> , RST_N,<br>I <sup>2</sup> C_SDA, I <sup>2</sup> C_SCL, IO1, IO2,<br>CLK | [2] |      | ± 2.0     | kV   |

| $V_{esd\_cdm}$                    | electrostatic discharge voltage<br>(Charge Device Model) | pads V <sub>CC</sub> , V <sub>SS</sub> , RST_N,<br>I <sup>2</sup> C_SDA, I <sup>2</sup> C_SCL, IO1, IO2,<br>CLK | [3] |      | ± 500     | V    |

| P <sub>tot</sub>                  | Total power dissipation                                  |                                                                                                                 | [4] | -    | 600       | mW   |

| T <sub>stg</sub>                  | Storage temperature                                      |                                                                                                                 |     | -55  | +125      | °C   |

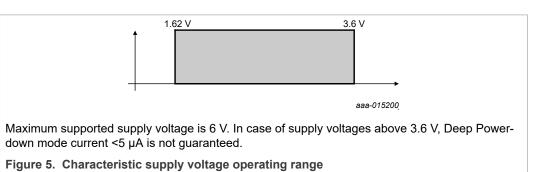

[1] Maximum supported supply voltage is 6 V. The SE050 is characterized for the specified operating supply voltage range of 1.62 V to 3.6 V. In case of supply voltages above 3.6 V, Deep Power-down mode current <5 µA is not guaranteed.</p>

[2] MIL Standard 883-D method 3015; human body model; C = 100 pF, R =  $1.5 \text{ k}\Omega$ ; T<sub>amb</sub> = -40 °C to +105 °C.

[3] JESD22-C101, JEDEC Standard Field induced charge device model test method.

[4] Depending on appropriate thermal resistance of the package.

# 13 Recommended operating conditions

The SE050 is characterized by its specified operating supply voltage range of 1.62 V to 3.6 V.

#### Table 9. Recommended operating conditions

| Symbol                            | Parameter      | Conditions             | Min  | Тур | Мах        | Unit |

|-----------------------------------|----------------|------------------------|------|-----|------------|------|

| V <sub>IN</sub> , V <sub>CC</sub> | Supply voltage | Nominal supply voltage | 1.62 | 1.8 | 3.6<br>[1] | V    |

| Symbol           | Parameter                                               | Conditions                      | Min  | Тур | Мах                                                        | Unit |

|------------------|---------------------------------------------------------|---------------------------------|------|-----|------------------------------------------------------------|------|

| VI               | DC input voltage on digital inputs and digital I/O pads | -                               | -0.3 |     | V <sub>CC</sub> /V <sub>IN</sub><br><sup>[2]</sup><br>+0.3 | V    |

| Н                | Field strength                                          | Contactless interface operation | 1.5  |     | 7.5                                                        | A/m  |

| T <sub>amb</sub> | Operating ambient temperature <sup>[3]</sup>            |                                 | -40  |     | +105                                                       | °C   |

#### Table 9. Recommended operating conditions...continued

Maximum supported supply voltage is 6 V. In case of supply voltages above 3.6 V, Deep Power-down mode current <5 µA is not guaranteed. [1]

IO1, CLK, RST has  $V_{CC}$  as reference, SDA, SCL, IO2 and ENA has  $V_{IN}$  as reference All product properties and values specified within this data sheet are only valid within the operating ambient temperature range. [2] [3]

# 14 Characteristics

#### 14.1 DC characteristics

#### Measurement conventions

Testing measurements are performed at the contact pads of the device under test. All voltages are defined with respect to the ground contact pad V<sub>SS</sub>. All currents flowing into the device are considered positive.

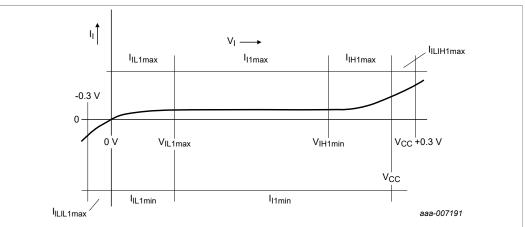

#### 14.1.1 General and General Purpose I/O interface

Table 10. Electrical DC characteristics of Input/Output: IO1/IO2. Conditions: V<sub>CC</sub> = 1.62 V to 3.6 V (see ; V<sub>SS</sub> = 0 V; T<sub>amb</sub> = -40 °C to + 105 °C, unless otherwise specified

In Table 10  $V_{CC}$  means for IO1 voltage on  $V_{CC}$  pin, for IO2 voltage on  $V_{IN}$  pin Maximum supported supply voltage is 6 V. In case of supply voltages above 3.6 V, Deep Power-down mode current <5 μA is not guaranteed.

| Symbol          | Parameter                                                | Conditions                                                                                                                                                                                     | Min                 | Тур | Max                   | Unit |

|-----------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----------------------|------|

| V <sub>IH</sub> | HIGH level input voltage                                 |                                                                                                                                                                                                | 0.7 V <sub>CC</sub> |     | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub> | LOW level input voltage                                  |                                                                                                                                                                                                | -0.3                |     | 0.25 V <sub>CC</sub>  | V    |

| IIH             | HIGH level input current in<br>"weak pull-up" input mode | $\begin{array}{l} 0.7 \ V_{CC} \leq V_{I} \leq V_{CC} \\ \text{Test conditions for the} \\ \text{maximum absolute} \\ \text{value: } I_{IH(max)} \\ V_{C}, \ V_{CC} = V_{CC(max)} \end{array}$ |                     |     | -20                   | μA   |

Table 10. Electrical DC characteristics of Input/Output: IO1/IO2. Conditions:  $V_{CC}$  = 1.62 V to 3.6 V (see ;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 °C to + 105 °C, unless otherwise specified...continued

In <u>Table 10</u>  $V_{CC}$  means for IO1 voltage on  $V_{CC}$  pin, for IO2 voltage on  $V_{IN}$  pin

Maximum supported supply voltage is 6 V. In case of supply voltages above 3.6 V, Deep Power-down mode current <5  $\mu$ A is not guaranteed.

| Symbol | Parameter                                                                                                   | Conditions                                                                                                                                                                                                           |     | Min | Тур | Мах   | Unit |

|--------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------|

| ΙL     | LOW level input current                                                                                     | $\begin{array}{l} 0 \ V \leq VI \leq 0.3 \ V_{CC}; \\ \hline \text{Test conditions for the} \\ \text{maximum} \\ \text{absolute value:} \\ I_{IL(max)}: V_I = 0 \ V, \ V_{CC} = \\ V_{CC(max)} \end{array}$          |     |     |     | -50   | μΑ   |

| TL     | HIGH-to-LOW transition<br>input current (only "quasi-<br>bidirectional" mode)                               | $\begin{array}{l} 0.3 \ V_{CC} < V_{I} \leq V_{CC}; \\ \text{Test conditions for the} \\ \text{maximum absolute} \\ \text{value: } V_{I} = 0.5 \ V_{CC}, \ V_{CC} \\ = V_{CC(max)} \end{array}$                      | [1] |     |     | -250  | μA   |

| I      | Input current in "weak pull-up"<br>input mode                                                               | $\begin{array}{l} 0 \ V_{\leq} \ V_{I} \leq V_{CC}; \ \text{Test} \\ \text{conditions for the} \\ \text{maximum absolute} \\ \text{value: } I_{I(max)} : V_{I} = 0 \ V, \\ V_{CC} = V_{CC(max)} \end{array}$         |     | 0   |     | -50   | μA   |

| Ιιιн   | Leakage input current at input<br>voltage beyond V <sub>CC</sub> in "weak<br>pull-up" input mode            | $V_{CC} < V_{I} \le V_{CC} + 0.3 V;$<br>-40 °C ≤<br>$T_{amb} \le +105 °C;$<br>Test conditions: V <sub>I</sub> = V <sub>CC</sub><br>+ 0.3<br>V;<br>$V_{CC} = V_{CC(max)}T_{amb} =$<br>+105 °C                         |     |     |     | 20    | μA   |

| ILIL   | Leakage input current at input<br>voltage below V <sub>SS</sub> in "weak<br>pull-up" input mode             | $\begin{array}{l} -0.3 \ V \leq V_{l} < 0 \ V; \ -40 \ ^{\circ}C \\ \leq T_{amb} \leq \\ +30 \ ^{\circ}C \\ Test \ conditions: \ V_{l} = -0.3 \\ V; \\ V_{CC} = V_{CC(max)}T_{amb} = \\ +30 \ ^{\circ}C \end{array}$ |     |     |     | -50   | μΑ   |

|        |                                                                                                             | $\begin{array}{l} -0.3 \ V \leq V_{I} < 0 \ V; +30 \ ^{\circ}C \\ \leq T_{amb} \leq \\ +105 \ ^{\circ}C \\ Test \ conditions: \ V_{I} = -0.3 \\ V; \\ V_{CC} = V_{CC(max)}T_{amb} = \\ +105 \ ^{\circ}C \end{array}$ |     |     |     | -1000 | μΑ   |

| lilihq | Leakage input current at<br>input voltage beyond V <sub>CC</sub><br>(only in "quasi-bidirectional"<br>mode) | $V_{CC} < V_{I} \le V_{CC} + 0.3 \text{ V};$<br>-40 °C ≤<br>$T_{amb} \le +105 \text{ °C}$<br>Test conditions: V <sub>I</sub> = V <sub>CC</sub><br>+                                                                  |     |     |     | 100   | μA   |

|        |                                                                                                             | 0.3 V;V <sub>CC</sub> = V <sub>CC(max)</sub> ;<br>T <sub>amb</sub> = +105 °C                                                                                                                                         |     |     |     |       |      |

© NXP B.V. 2020. All rights reserved.

504931

Table 10. Electrical DC characteristics of Input/Output: IO1/IO2. Conditions:  $V_{CC}$  = 1.62 V to 3.6 V (see ;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 °C to + 105 °C, unless otherwise specified...*continued*

In <u>Table 10</u>  $V_{CC}$  means for IO1 voltage on  $V_{CC}$  pin, for IO2 voltage on  $V_{IN}$  pin

Maximum supported supply voltage is 6 V. In case of supply voltages above 3.6 V, Deep Power-down mode current <5  $\mu$ A is not guaranteed.

| Symbol             | Parameter                                                                                                  | Conditions                                                                                                                                                                                                           |     | Min                 | Тур | Max                         | Unit |

|--------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------|-----|-----------------------------|------|

| I <sub>ILILQ</sub> | Leakage input current at input<br>voltage below V <sub>SS</sub> (only in<br>"quasi-bidirectional"<br>mode) | $\begin{array}{l} -0.3 \ V \leq V_{I} < 0 \ V; \ -40 \ ^{\circ}C \\ \leq T_{amb} \leq \\ +30 \ ^{\circ}C \\ Test \ conditions: \ V_{I} = -0.3 \\ V; \\ V_{CC} = V_{CC(max)}T_{amb} = \\ +30 \ ^{\circ}C \end{array}$ |     |                     |     | -120                        | μΑ   |

|                    |                                                                                                            | $\begin{array}{l} -0.3 \ V \leq V_{I} < 0 \ V; +30 \ ^{\circ}C \\ \leq T_{amb} \leq \\ +105 \ ^{\circ}C \\ Test \ conditions: \ V_{I} = -0.3 \\ V; \\ V_{CC} = V_{CC(max)}T_{amb} = \\ +105 \ ^{\circ}C \end{array}$ |     |                     |     | -1000                       | μΑ   |

| V <sub>OH</sub>    | HIGH level output voltage                                                                                  | I <sub>OH</sub> = -20 μA;                                                                                                                                                                                            | [2] | 0.7 V <sub>CC</sub> |     |                             | V    |

| V <sub>OL</sub>    | LOW level output voltage                                                                                   | I <sub>OL</sub> = 1.0 mA<br>I <sub>OL</sub> = 0.5 mA                                                                                                                                                                 |     |                     |     | 0.3<br>0.15 V <sub>CC</sub> | V    |

[1] IO1/IO2 source a transition current when being externally driven from HIGH to LOW. This transition current (I<sub>TL</sub>) reaches its maximum value when the input voltage V<sub>I</sub> is approximately 0.5 V<sub>CC</sub>. Current IIL is tested at input voltage V<sub>I</sub> = 0.3 V.

[2] External pull-up resistor 20 k $\Omega$  to V<sub>CC</sub> assumed. The worst case test condition for parameter V<sub>OH</sub> is present at minimum V<sub>CC</sub>.

# SE050

### Plug & Trust Secure Element

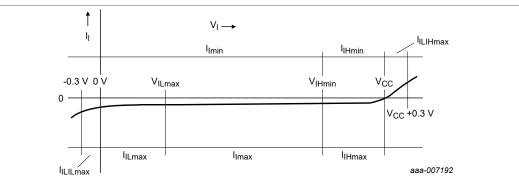

# 14.1.2 I<sup>2</sup>C Interface

Table 11. Electrical DC characteristics of I<sup>2</sup>C pads SDA, SCL. Conditions:  $V_{CC}$ ,  $V_{IN}$  = 1.62 V to 3.6 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 °C to + 105 °C, unless otherwise specified\*

Maximum supported supply voltage is 6 V. In case of supply voltages above 3.6 V, Deep Power-down mode current <5  $\mu$ A is not guaranteed.

SCL, SDA pads are in open-drain mode.

| Symbol              | Parameter                                  | Conditions                                            | Min                 | Тур  | Max                   | Unit |

|---------------------|--------------------------------------------|-------------------------------------------------------|---------------------|------|-----------------------|------|

| V <sub>IH</sub>     | HIGH level input voltage                   |                                                       | 0.7 V <sub>IN</sub> |      | V <sub>IN</sub> + 0.3 | V    |

| V <sub>IL</sub>     | LOW level input voltage                    |                                                       | -0.3                |      | 0.25 V <sub>IN</sub>  | V    |

| V <sub>HYS</sub>    | Input hysteresis voltage                   | -                                                     | 0.081 V             |      |                       | V    |

| V <sub>OL(OD)</sub> | Low level output voltage (open-drain mode) | I <sub>OL</sub> = 3.0 mA                              | 0                   |      | 0.4                   | V    |

| I <sub>OL(OD)</sub> | Low level output current (open-drain mode) | V <sub>OL</sub> = 0.6 V                               | 0.6                 |      |                       | mA   |

| I <sub>WPU</sub>    | weak pull-up current                       | V <sub>IO</sub> = 0 V                                 | -265                | -180 | -70                   | μA   |

| I <sub>ILIH</sub>   | Leakage input current high level           | V <sub>SDA</sub> = 3.6 V, V <sub>SCL</sub> = 3.6<br>V |                     | 0.27 | 15                    | μA   |

#### 14.1.3 Power consumption

#### Table 12. Electrical characteristics of IC supply voltage V<sub>CC</sub>; V<sub>SS</sub> = 0 V; T<sub>amb</sub> = -40 °C to +105 C

| Symbol                           | Parameter                                                                            | Conditions                                                                                                                                           | Min  | Тур  | Мах  | Unit |

|----------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Supply                           | L                                                                                    | 1                                                                                                                                                    |      |      |      |      |

| V <sub>CC</sub>                  | supply voltage range                                                                 | V <sub>CC</sub> = 1.62 - 3.6 V                                                                                                                       | 1.62 | 1.80 | 3.6  | V    |

|                                  | operating mode: Idle mode                                                            |                                                                                                                                                      |      |      |      |      |

| I <sub>DD</sub> <sup>[1]</sup>   | operating mode: typical CPU                                                          |                                                                                                                                                      |      |      |      |      |

|                                  | no coprocessor active                                                                | f <sub>CPU</sub> = 48 MHz, f <sub>MST</sub> = 96 MHz                                                                                                 |      | 4.4  | 7    | mA   |

|                                  | AES coprocessor active<br>(AES 48 MHz)                                               | CPU in idle mode                                                                                                                                     |      | 6.5  | 7.5  | mA   |

|                                  | Public Key cryptography Coprocessor<br>active<br>(96 MHz)                            | CPU in idle mode                                                                                                                                     |      | 14.4 | 16.1 | mA   |

|                                  | DES coprocessor active<br>(DES 48 MHz)                                               | CPU in idle mode                                                                                                                                     |      | 6.5  | 7.6  | mA   |

| I <sub>DD (PD-</sub><br>ISO7816) | supply current Power-down mode<br>(ISO7816 clock-stop)                               | $V_{CCmin} \le V_{CC} \le V_{CCmax}$ ; Clock to<br>input CLK stopped, $T_{amb}$ = 25 °C                                                              |      | 430  | 480  | μA   |

| I <sub>DDD (DPD)</sub>           | supply current Deep Power-down mode                                                  | V <sub>CCmin</sub> ≤ V <sub>IN</sub> ≤ V <sub>CCmax;</sub> T <sub>amb</sub> =<br>25 °C                                                               |      | 3    | 5    | μA   |

| I <sub>DD</sub> (PD-I2C)         | supply current I <sup>2</sup> C Power-down mode<br>(I <sup>2</sup> C wake-up source) | $V_{CCmin} \le V_{CC} \le V_{CCmax}$ ; Clock<br>to input SCL stopped, Tamb=<br>25 °C SDA, SCL pads in pull-up<br>Typical value with $V_{CC}$ = 1.8 V |      | 450  | 500  | μA   |

[1] Maximum current consumption with concurrent AES and Public Key Cryptography 19 mA.

SE050 Product data sheet

#### **14.2 AC characteristics**

#### Table 13. Non-volatile memory timing characteristics

Conditions:  $V_{CC}$  = 1.62 V to 3.6 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 °C to +105 °C, unless otherwise specified.

| Symbol           | Parameter                                                                                                                                                           | Conditions                |     | Min                  | Typ <sup>[1]</sup>       | Мах | Unit   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|----------------------|--------------------------|-----|--------|

| t <sub>EEP</sub> | FLASH erase + program time                                                                                                                                          |                           | [2] |                      | 2.3                      |     | ms     |

| t <sub>EEE</sub> | FLASH erase time                                                                                                                                                    |                           |     |                      | 0.9                      |     | ms     |

| t <sub>EEW</sub> | FLASH program time                                                                                                                                                  |                           |     |                      | 1.4                      |     | ms     |

| t <sub>EER</sub> | FLASH data retention time                                                                                                                                           | T <sub>amb</sub> = +55 °C |     | 25                   |                          |     | years  |

| N <sub>EEC</sub> | FLASH endurance (maximum<br>number of programming cycles<br>applied to the whole memory<br>block performed by NXP static<br>and dynamic wear leveling<br>algorithm) |                           |     | 20 × 10 <sup>6</sup> | 100 ×<br>10 <sup>6</sup> |     | cycles |

[1] Typical values are only referenced for information. They are subject to change without notice.

[2] Given value specifies physical access times of FLASH memory only.

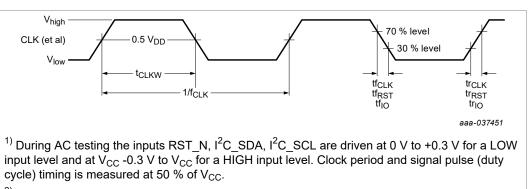

# Table 14. Electrical AC characteristics of $I^2C\_SDA$ , $I^2C\_SCL$ , and RST $\_N^{[1]}$ ; $V_{CC} = 1.8 \text{ V} \pm 10 \% \text{ or } 3 \text{ V} \pm 10 \% \text{ V}$ ; $V_{SS} = 0 \text{ V}$ ; $T_{amb} = -40 \text{ °C}$ to + 105 °C

SCL, SDA pads in open-drain mode.

| Symbol             | Parameter                                                                               | Conditions                                                                     |     | Min | Тур | Мах  | Unit |

|--------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-----|-----|-----|------|------|

| Input/Ou           | Itput: I <sup>2</sup> C_SDA, I <sup>2</sup> C_SCL in ope                                | n-drain mode                                                                   |     |     | 1   |      |      |

| tr <sub>IO</sub>   | I/O Input rise time                                                                     | Input/reception mode                                                           | [2] |     |     | 1    | μs   |

| tf <sub>IO</sub>   | I/O Input fall time                                                                     | Input/reception mode                                                           | [2] |     |     | 1    | μs   |

| tf <sub>OIO</sub>  | I/O Output fall time                                                                    | Output/transmission mode; C <sub>L</sub><br>= 30 pF                            | [2] |     |     | 0.3  | μs   |

| f <sub>CLK</sub>   | External clock frequency in I <sup>2</sup> C applications                               | $t_{CLKW},T_{amb}$ and $V_{CC}$ in their specified limits                      |     | -   |     | 3.4  | MHz  |

| t <sub>PD</sub>    | Power down duration time (I <sup>2</sup> C wake-up)                                     | CPU clock = 48 MHz                                                             | [3] |     | 67  |      | μs   |

| t <sub>WKPD</sub>  | Wake-up from power down duration time (I <sup>2</sup> C wake-up)                        | CPU clock = 48 MHz                                                             | [4] |     | 97  |      | μs   |

| C <sub>PIN</sub>   | Pin capacitances RST_N,<br>I <sup>2</sup> C_SDA, /I <sup>2</sup> C_SCL                  | Test frequency = 1 MHz; Tamb<br>= 25 °C                                        |     | -   |     | 10.5 | pF   |

| t <sub>ENalt</sub> | ENA low time and Vout, V <sub>cc</sub><br>low time for entering deep<br>power down mode |                                                                                | [5] |     | 2   |      | μs   |

| R <sub>on</sub>    | Resistance of power switch                                                              | T <sub>amb</sub> =105 °C, I <sub>load</sub> =25 mA,<br>V <sub>in</sub> =1.62 V |     |     |     | 1.1  | Ohm  |

| l <sub>out</sub>   | maximum current driving capability of pin V <sub>out</sub>                              | T <sub>amb</sub> =105 °C                                                       |     |     |     | 25   | mA   |

Table 14. Electrical AC characteristics of  $I^2C\_SDA$ ,  $I^2C\_SCL$ , and RST $\_N^{[1]}$ ;  $V_{CC} = 1.8 \text{ V} \pm 10 \% \text{ or } 3 \text{ V} \pm 10 \% \text{ V}$ ;  $V_{SS} = 0 \text{ V}$ ;  $T_{amb} = -40 \text{ °C}$  to + 105 °C*...continued*

SCL, SDA pads in open-drain mode.

| Symbol              | Parameter                                                              | Conditions                                          | Min | Тур | Max  | Unit |

|---------------------|------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|------|------|

| t <sub>RW</sub>     | Reset pulse width (RST_N low)<br>without entering Power-down<br>mode   |                                                     | 40  |     | 400  | μs   |

| t <sub>RDSLP</sub>  | Reset pulse width (RST_N low) to enter Power-down mode                 |                                                     | 500 |     |      | μs   |

| t <sub>WKP</sub>    | Wake-up time from Power-<br>down mode                                  | $f_{CLKmin} < f_{CLK} < f_{CLKmax}$                 | -   | 8   | 10   | μs   |

| t <sub>WKPIO</sub>  | Pad LOW time for wake-up                                               | level triggered ext.int.                            | -   | 8   | 10   | μs   |

|                     | from Power-down mode                                                   | edge triggered ext.int.                             | -   | 8   | 10   | μs   |

| t <sub>WKPRST</sub> | RST_N LOW time for wake-up<br>from Power-down mode                     |                                                     | 40  |     | -    | μs   |

| C <sub>PIN</sub>    | Pin capacitances RST_N,<br>I <sup>2</sup> C_SDA, /I <sup>2</sup> C_SCL | Test frequency = 1 MHz; T <sub>amb</sub><br>= 25 °C | -   |     | 10.5 | pF   |

[1] All appropriately marked values are typical values and only referenced for information. They are subject to change without notice.

[2]  $t_r$  is defined as rise time between 30 % and 70 % of the signal amplitude.

$t_{\rm f}$  is defined as fall time between 70 % and 30 % of the signal amplitude.

[3] Wakeup from power down: if clock stretching disabled and I<sup>2</sup>C\_SCL=400 kHz; the wakeup time will not be sufficient under the rare condition where host sends the first command during the time where SE is just entering power down; in this case the SE will send an R block to request retransmission from the host

[4] Wakeup from power down: if clock stretching disabled and I<sup>2</sup>C\_SCL=1 MHz; the wakeup time will not be sufficient to receive the first host command; the SE will send an R block to request retransmission from the host

[5] Low glitches below 0.4 V on pin ENA and Vin, Vout, Vcc larger than 30 ns cause Power-On-Reset, respectively entering deep power-down mode.

$^{2)}$  t<sub>r</sub> is defined as rise time between 30 % and 70 % of the signal amplitude. tf is defined as fall time between 70 % and 30 % of the signal amplitude.

Figure 10. External clock drive and AC test timing reference points of  $I^2C\_SDA$ ,  $I^2C\_SCL$ , and RST\_N (see <sup>1)</sup> and <sup>2)</sup>) in open-drain mode

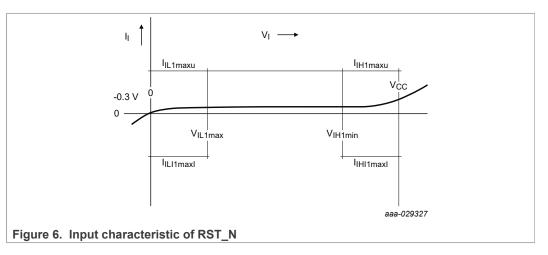

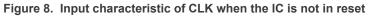

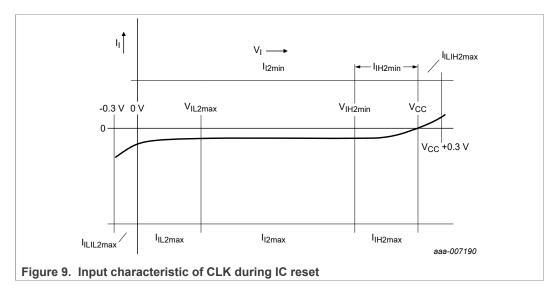

Table 15. Electrical AC characteristics of IO1, IO2, CLK and RST\_N (ISO7816 interface)Conditions:  $V_{CC} = 1.8 V \pm 10 \%$  or  $3 V \pm 10 \% V$ ;  $V_{SS} = 0 V$ ;  $T_{amb} = -40 \degree C$  to  $+105 \degree C$ , unless otherwise specified. Typicalvalues are only referenced for information. They are subject to change without notice.

| Symbol                | Parameter           | Conditions           |            | Min | Тур | Мах | Unit |  |  |  |

|-----------------------|---------------------|----------------------|------------|-----|-----|-----|------|--|--|--|

| Input/Output: IO1/IO2 |                     |                      |            |     |     |     |      |  |  |  |

| tr <sub>IO</sub>      | I/O Input rise time | Input/reception mode | [1]<br>[2] |     |     | 1   | μs   |  |  |  |

| 02000   |      |       |

|---------|------|-------|

| Product | data | sheet |

Table 15. Electrical AC characteristics of IO1, IO2, CLK and RST\_N (ISO7816 interface)...continued Conditions:  $V_{CC} = 1.8 \text{ V} \pm 10 \%$  or  $3 \text{ V} \pm 10 \%$  V;  $V_{SS} = 0 \text{ V}$ ;  $T_{amb} = -40 \degree \text{C}$  to  $+105 \degree \text{C}$ , unless otherwise specified. Typical values are only referenced for information. They are subject to change without notice.

| Symbol            | Parameter                                                                      | Conditions                                                                     |            | Min  | Тур | Max                             | Unit |

|-------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------|------|-----|---------------------------------|------|

|                   |                                                                                |                                                                                | [3]<br>[2] |      |     | 0.25 x<br>t <sub>IOWx_min</sub> | μs   |

| tf <sub>IO</sub>  | I/O Input fall time                                                            | Input/reception mode                                                           | [1]<br>[2] |      |     | 1                               | μs   |

|                   |                                                                                |                                                                                | [3]<br>[2] |      |     | 0.25 x<br>t <sub>IOWx_min</sub> | μs   |

| tr <sub>OIO</sub> | I/O Output rise time                                                           | Output/transmission mode; CL<br>= 30 pF                                        | [2]        |      |     | 0.1                             | μs   |

| tf <sub>OIO</sub> | I/O Output fall time                                                           | Output/transmission mode; CL<br>= 30 pF                                        | [2]        |      |     | 0.1                             | μs   |

| Inputs: (         | CLK and RST_N                                                                  |                                                                                |            |      |     | I                               |      |

| f <sub>CLK</sub>  | External clock frequency<br>in ISO/IEC 7816 UART<br>applications               | $t_{\text{CLKW}},t_{\text{amb}}$ and $V_{\text{CC}}$ in their specified limits | [4]        | 0.85 |     | 11.5                            | MHz  |

| t <sub>CLKW</sub> | Clock pulse width i.r.t. clock<br>period (positive pulse duty<br>cycle of CLK) |                                                                                |            | 40   |     | 60                              | %    |

| tr <sub>CLK</sub> | CLK input rise time                                                            |                                                                                | [5]        |      |     | [6]                             |      |

| tf <sub>CLK</sub> | CLK input fall time                                                            |                                                                                | [2]<br>[6] |      |     | [6]                             |      |

| tr <sub>RST</sub> | RST_N input rise time                                                          |                                                                                | [2]        |      |     | 400                             | μs   |

| tf <sub>RST</sub> | RST_N input fall time                                                          |                                                                                | [2]<br>[7] |      |     | 400                             | μs   |

At minimum IO1 input signal HIGH or LOW level voltage pulse width of 3.2 µs. This timing specification applies to ISO7816 configurations down to a [1] minimum etu duration of 16 CLK cycles at a maximum CLK frequency of 5 MHz (TA1=0x96, (Fi/Di)=(512/32)), for example.

tr is defined as rise time between 10 % and 90 % of the signal amplitude. [2]

At minimum IO1 input signal HIGH or LOW level voltage pulse width of less than 3.2 µs. This timing specification applies to ISO7816 configurations [3] beyond the conditions listed in note [2], down to a minimum etu duration of 8 CLK cycles at a maximum CLK frequency of 5 MHz (TA1=0x97, (Fi/ Di)=(512/64)), for example. An 8 CLKs/etu @ fclk = 5 MHz configuration results in tIOWx\_min = 1.6 µs, and in a time of 400 ns for trIO\_max and tfIO\_ max, matching the (Fi/Di)=(512/64) speed enhancement requirements of ETSI TS 102 221.

ISO/IEC 7816 I/O applications have to supply a clock signal to input CLK in the frequency range of 1 MHz to 10 MHz nominal. A ± 15 % tolerance range [4] yields the allowed limits of 0.85 MHz and 11.5 MHz.

During AC testing the inputs CLK, RST\_N, and IO1 are driven at 0 V to +0.3 V for a LOW input level and at V<sub>CC</sub> - 0.3 V to V<sub>CC</sub> for a HIGH input level. [5] Clock period and signal pulse (duty cycle) timing is measured at 50 % of V<sub>CC</sub>, see Figure 18.

The maximum CLK rise and fall time is 10 % of the CLK period 1/fCLK - with the following exception: In the CLK frequency range of 1 MHz to 5 MHz the [6] maximum allowed CLK rise and fall time is 50 ns, if 10 % of the CLK period is shorter than 50 ns. [7]

The ETSI TS102 221/GSM 11.1x specifications specify a maximum reset signal (RST\_N) rise time and fall time of 400,000 µs, respectively.

Note: tf is defined as fall time between 90 % and 10 % of the signal amplitude.

Table 16. Electrical AC characteristics of LA, LB; Conditions: Tamb = -40 °C to 105 °C, unless otherwise specified

Conditions: T<sub>amb</sub> = -25 °C to +85 °C, unless otherwise specified.

| Symbol               | Parameter | Conditions | Typ <sup>[1]</sup> | Max | Unit |

|----------------------|-----------|------------|--------------------|-----|------|

| Input/Output: LA, LB |           |            |                    |     |      |

**Product data sheet**

SE050

© NXP B.V. 2020. All rights reserved

Table 16. Electrical AC characteristics of LA, LB; Conditions: Tamb = -40 °C to 105 °C, unless otherwise specified...continued

Conditions: T<sub>amb</sub> = -25 °C to +85 °C, unless otherwise specified.

| Symbol                           | Parameter                                                                                                          | Conditions                                                           |                | Typ <sup>[1]</sup> | Max | Unit |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------|--------------------|-----|------|

| C <sub>LALB</sub> <sup>[2]</sup> | Pin capacitance LA, LB<br>Bare die (SO28 empty package<br>ground-off)                                              |                                                                      |                |                    |     |      |

|                                  | Configured for antenna input with<br>56 pF capacitance<br>Test frequency = 13.56 MHz;<br>T <sub>amb</sub> = 25 °C  | V <sub>LA,LB</sub> = 2.1 V (rms)<br>V <sub>LA,LB</sub> = 0.3 V (rms) | [3] [4]<br>[4] | 54.3<br>50.1       |     | pF   |

| R <sub>LALB</sub> <sup>[2]</sup> | Configured for antenna input with<br>56 pF capacitance. Test frequency<br>= 13.56 MHz;<br>T <sub>amb</sub> = 25 °C | V <sub>LA,LB</sub> = 2.1 V (rms)                                     | [3] [4]<br>[5] | 0.913              |     | kΩ   |

| f <sub>LALB</sub>                | Operating frequency LA, LB                                                                                         | level triggered ext.int.                                             |                | 13.56              |     | MHz  |

Typical values ( $\pm$  10 %) are only referenced for information. They are subject to change without notice. The CLALB and RLALB values stated here assume a parallel RC equivalent circuit for the chip. [1]

[2] [3] The value stated here was measured at estimated start of chip operation and is comparable to the values stated in other SmartMX3 family member data sheets.

Measured with sine wave at LA, LB. [4]

Parameter is valid in contactless ISO14443 compliant operation valid only. [5]

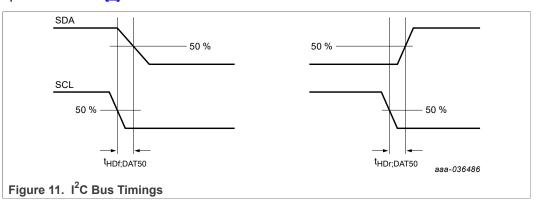

# 14.3 I<sup>2</sup>C Bus Timings

Parameters defined in this chapter replace the parameter definitions of  $I^2C$  bus, for specification see [4].

| Symbol                                | Parameter                                 | Condition | Min | Мах | Unit |

|---------------------------------------|-------------------------------------------|-----------|-----|-----|------|

| t <sub>HDf;DAT50</sub> <sup>[1]</sup> | data hold time<br>50% SCL - 50% SDA level | Fast mode | 8   |     | ns   |

| t <sub>HDr;DAT50</sub> <sup>[2]</sup> | data hold time<br>50% SCL - 50% SDA level | Fast mode | 24  |     | ns   |

| t <sub>HDf;DAT50</sub> <sup>[1]</sup> | data hold time<br>50% SCL - 50% SDA level | Hs mode   | 8   |     | ns   |

| t <sub>HDr;DAT50</sub> [2]            | data hold time<br>50% SCL - 50% SDA level | Hs mode   | 9   |     | ns   |

# Table 17. I<sup>2</sup>C Bus Timing Specification

$t_{HDf;DAT50}$ , as defined in <u>Figure 11</u>, replaces parameter  $t_{HD;DAT}$  defined in [4]  $t_{HDr;DAT50}$ , as defined in <u>Figure 11</u>, replaces parameter  $t_{HD;DAT}$  defined in [4] [1] [2]

#### 14.4 EMC/EMI

EMC and EMI resistance according to IEC 61967-4.

# 15 Abbreviations

| Table 18. Abbre | viations                                |

|-----------------|-----------------------------------------|

| Acronym         | Description                             |

| AES             | Advanced Encryption Standard            |

| APDU            | Application Protocol Data Unit          |

| CL              | Contactless                             |

| CLK             | External clock signal input contact pad |

| CC              | Common Criteria                         |

| CMAC            | Cipher-based MAC                        |

| CRC             | Cyclic Redundancy Check                 |

| CRI             | Cryptography Research Incorporated      |

| DES             | Digital Encryption Standard             |

| DPA             | Differential Power Analysis             |

| DSS             | Digital Signature Standard              |

| EAL             | Evaluation Assurance Level              |

| ECC             | Elliptic Curve Cryptography             |

| EMC             | Electromagnetic compatibility           |

| EMI             | Electro Magnetic Immunity               |

| FM              | Fast-Mode                               |

| FM+             | Fast-Mode+                              |

| GP              | Global Platform                         |

| GPIO            | General-purpose input/output            |

| HS              | High-Speed-Mode                         |

SE050

Plug & Trust Secure Element

| viationscontinued                                     |

|-------------------------------------------------------|

| Description                                           |

| HMAC-based Extract-and-Expand Key Derivation Function |

| Keyed-Hash Message Authentication Code                |

| Hardware                                              |

| Integrated Circuit                                    |

| Inter-Integrated Circuit                              |

| Input/Output                                          |

| Internet of Things                                    |

| Java Card Open Platform                               |

| ISO 14443 Antenna Pad                                 |

| ISO 14443 Antenna Pad                                 |

| Near Field Communication                              |

| Message Authentication Code                           |

| Microcontroller unit                                  |

| Microprocessor                                        |

| Middleware                                            |

| Operating System                                      |

| National Institute for Standards and Technology       |

| Protocol Control Byte                                 |

| Public Key Infrastructure                             |

| Pseudo Random Function                                |

| Random Access Memory                                  |

| Rivest-Shamir-Adleman                                 |

| Reset                                                 |

| Secure Access Module                                  |

| Serial clock                                          |

| Serial data                                           |

| Simple Power Analysis                                 |

| Single Fault Injection                                |

| Secure Hash Algorithm                                 |

| Software                                              |

| Transport Layer Security                              |

| Supply Voltage Input                                  |

| Voltage Input                                         |

| Voltage Output                                        |

| Ground                                                |

|                                                       |

Table 18. Abbreviations...continued

SE050 Product data sheet

# **16 References**

- [1] NXP SE05x T=1 Over I<sup>2</sup>C Specification User manual, document number UM11225. Available on <u>NXP website</u>

- [2] SOT1969-1; HX2QFN20; Reel packing and package information. Available on <u>NXP</u> website

- [3] SE050 IoT Applet APDU Specification, document number AN 12413. Available on NXP website

- [4] SE050 configurations Application Note, document number AN12436. Available on NXP website

504931

# 17 Revision history